ANALOG & RF | INTERFACE & CONNECTIVITY |

# VersaClock® III Programmable Clocks

CLOCKS & TIMING | MEMORY & LOGIC | TOUCH & USER INTERFACE | VIDEO & DISPLAY | AUDIO

#### **KEY FEATURES**

- 3.3V device with up to four independently controlled VDDO (1.8V - 3.3V)

- Two of four integrated PLLs support spread spectrum generation for EMI reduction

- Integrated VCXO

- Output frequency range: 4.9 kHz to 500 MHz

- 1.8 3.3 V LVTTL/ LVCMOS

- LVPECL, LVDS and HCSL

- Programmable loop bandwidth

- Programmable slew rate control,

- Redundant clock inputs with glitchless auto and manual switchover options

- Small 4x4mm and 5x5mm QFN and TSSOP packages

## VERSACLOCK III SOFTWARE OPTIMIZES CONFIGURATIONS

- Automatic analysis and adjustment of spread spectrum, loop bandwidths and outputs

- Provides clock to pin locking and multi-register configuration

- · Bit-level manipulation

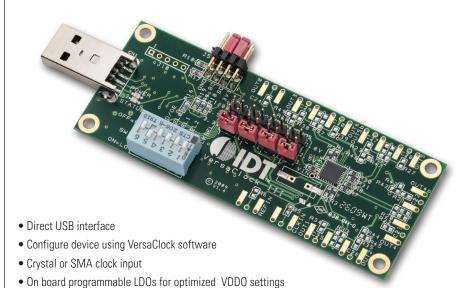

- Direct software interface with VersaClock III evaluation board

- Free download from www.idt.com/go/versaclock3

IDT VersaClock products save cost, reduce board space and greatly increase versatility in consumer, data communications, telecommunications and networking applications.

#### Multi purpose clock provides many solutions

VersaClock® products allow designers to save board space and cost by replacing crystals, oscillators and buffers with a single timing device. Exceptional versatility and configurability allow for maximum freedom in the design process.

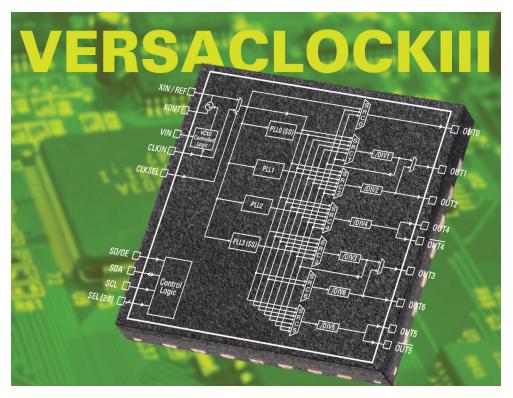

There are four internal PLLs, each individually programmable, allowing for up to seven unique frequencies. These frequencies are generated from a single reference clock, which can come from one of two redundant clock inputs. A glitchless automatic or manual switchover function allows the redundant clock to be selected during normal operation.

VersaClock devices are highly configurable and can be programmed through the use of the  $l^2C$  interface. The programming interface enables the device to be programmed when it is in normal operation. An internal EEPROM allows the user to save and restore the configuration of the device without having to reprogram it on power-up.

VersaClock products from IDT provide an almost universal solution for a variety of high performance clock applications.

### VersaClock® III Programmable Clocks

ER MANAGEMENT | ANALOG & RF | INTERFACE & CONNECTIVITY | CLOCKS & TIMING | MEMORY & LOGIC | TOUCH & USER INTERFACE | VIDEO & DISPLAY | AUDIO

#### **VERSACLOCK III EVALUATION BOARD**

- Matched differential output traces

- Multiple daughtercards with sockets available to program additional devices

#### **FEATURES**

- Four internal PLLs

- Optional integrated VCXO

- Internal non-volatile EEPROM

- Each PLL has a 7-bit reference divider and a 12-bit feedback divider

- Fast (400 kHz) mode I2C serial interface for device configuration

- 8-bit output divider clocks

- Output frequency range: 4.9 kHz to 500 MHz

- Programmable loop bandwidth settings

- Input clock frequency range: 1 MHz to 200 MHz

- Programmable output inversion to reduce jitter

- Reference crystal input with programmable linear load capacitance

- Crystal frequency range: 8 to 50 MHz

- I / O Standards:

- Outputs 1.8/2.5/3.3 V LVTTL / LVCMOS (device dependent)

- Outputs LVPECL, LVDS and HCSL

- Inputs LVTTL / LVCMOS

- Two PLLs support spread spectrum generation

- · Redundant clock inputs with glitch-less auto switchover

- Fractional divide capability on one PLL

- -40 to +85°C industrial temperature operation

| VersaClock III Parts |                        |            |                           |         |

|----------------------|------------------------|------------|---------------------------|---------|

| ХO                   | Package                | Output No. | Output Type               | VDDO    |

| 5V49EE901            | TSSOP28, QFN32 (5x5mm) | 9          | LVTTL, LVPECL, LVDS, HCSL | No      |

| 5V49EE902            | QFN32 (5x5mm)          | 9          | LVTTL, LVPECL, LVDS, HCSL | Yes - 4 |

| 5V49EE903            | TSSOP28, QFN32 (5x5mm) | 9          | LVTTL                     | No      |

| 5V49EE904            | QFN32 (5x5mm)          | 9          | LVTTL                     | Yes - 4 |

| 5V49EE701            | QFN28 (4x4mm)          | 7          | LVTTL, LVPECL, LVDS, HCSL | No      |

| 5V49EE702            | QFN28 (4x4mm)          | 7          | LVTTL, LVPECL, LVDS, HCSL | Yes - 3 |

| 5V49EE703            | QFN28 (4x4mm)          | 7          | LVTTL                     | No      |

| 5V49EE704            | QFN28 (4x4mm)          | 7          | LVTTL                     | Yes -3  |

| 5V49EE501            | QFN24 (4x4mm)          | 5          | LVTTL, LVPECL, LVDS, HCSL | No      |

| 5V49EE502            | QFN24 (4x4mm)          | 5          | LVTTL, LVPECL, LVDS, HCSL | Yes -2  |

| 5V49EE503            | QFN24 (4x4mm)          | 5          | LVTTL                     | No      |

| 5V49EE504            | QFN24 (4x4mm)          | 5          | LVTTL                     | Yes - 2 |

| VCXO                 | Package                | Output No  | Output Type               | VDDO    |

| 5V19EE901            | TSSOP28, QFN32 (5x5mm) | 9          | LVTTL, LVPECL, LVDS, HCSL | No      |

| 5V19EE902            | QFN32 (5x5mm)          | 9          | LVTTL, LVPECL, LVDS, HCSL | Yes - 4 |

| 5V19EE903            | TSSOP28, QFN32 (5x5mm) | 9          | LVTTL                     | No      |

| 5V19EE904            | QFN32 (5x5mm)          | 9          | LVTTL                     | Yes - 4 |

| 5V19EE603            | QFN28 (4x4mm)          | 6          | LVTTL                     | No      |

| 5V19EE604            | QFN28 (4x4mm)          | 6          | LVTTL                     | Yes - 3 |

| 5V19EE403            | QFN24 (4x4mm)          | 4          | LVTTL                     | No      |

| 5V19EE404            | QFN24 (4x4mm)          | 4          | LVTTL                     | Yes - 2 |

Discover what IDT know-how can do for you: www.IDT.com/go/versaclock3

PB\_VERSACLOCK III\_REVC0611

IDT | THE ANALOG + DIGITAL COMPANY VERSACLOCK III PRODUCT BRIEF 2