# M68ICS08JB In-Circuit Simulator

#### **Important Notice to Users**

While every effort has been made to ensure the accuracy of all information in this document, Motorola assumes no liability to any party for any loss or damage caused by errors or omissions or by statements of any kind in this document, its updates, supplements, or special editions, whether such errors are omissions or statements resulting from negligence, accident, or any other cause. Motorola further assumes no liability arising out of the application or use of any information, product, or system described herein: nor any liability for incidental or consequential damages arising from the use of this document. Motorola disclaims all warranties regarding the information contained herein, whether expressed, implied, or statutory, including implied warranties of merchantability or fitness for a particular purpose. Motorola makes no representation that the interconnection of products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting or license to make, use or sell equipment constructed in accordance with this description.

#### **Trademarks**

This document includes these trademarks:

Motorola and the Motorola logo are registered trademarks of Motorola. Inc.

Windows and Windows 95 are registered trademarks of Microsoft Corporation in the U.S. and other countries.

Intel is a registered trademark of Intel Corporation.

Motorola, Inc., is an Equal Opportunity / Affirmative Action Employer.

For an electronic copy of this book, visit Motorola's web site at http://mcu.motsps.com/documentation © Motorola, Inc., 2000; All Rights Reserved

User's Manual

M68ICS08JB In-Circuit Simulator

2 MOTOROLA

# User's Manual — M68ICS08JB In-Circuit Simulator

# **Table of Contents**

# **Section 1. General Information**

| 1.1                                                       | Introduction                                                                                                                                                                                      | 1                |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1.2<br>1.2.1<br>1.2.2                                     | JBICS Components14JBICS Hardware15ICS Interface Software16                                                                                                                                        | 5                |

| 1.3                                                       | Hardware and Software Requirements                                                                                                                                                                | 6                |

| 1.4                                                       | Specifications                                                                                                                                                                                    | 7                |

| 1.5                                                       | About This Manual                                                                                                                                                                                 | 7                |

| 1.6                                                       | Customer Support                                                                                                                                                                                  | 7                |

|                                                           | Section 2. Preparation and Installation                                                                                                                                                           |                  |

| 2.1                                                       | Introduction                                                                                                                                                                                      | 9                |

| 2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6 | Hardware Preparation19JBICS Limitations20Configuring JBICS Jumper Headers20Target Interface Connection Options22Host Computer - JBICS Interconnection (P2)22Power Connector (P1)22USB Connector24 | 0<br>0<br>2<br>3 |

| 2.3                                                       | Connecting the JBICS                                                                                                                                                                              | 5                |

| 2.4                                                       | Connecting the JBICS to the Target System                                                                                                                                                         | 5                |

| 2.5                                                       | Installing the Software                                                                                                                                                                           | 6                |

|                                                           | Section 3. Support Information                                                                                                                                                                    |                  |

| 3.1                                                       | Introduction                                                                                                                                                                                      | 7                |

M68ICS08JB In-Circuit Simulator

# **Table of Contents**

| 3.3.     JBICS Functional Description     27       3.3.1     ICS08JB Board     28       3.3.2     Clock Selection     29       3.3.3     Board Reset     29       3.3.4     Device Configuration Selection     30       3.3.5     Level Translation     30       3.3.6     Host System Connector     31       3.3.7     USB Interface     31       3.4.1     Target Flex Cable Interface Connectors J1 and J2     32       3.4.2     J3 DIP Connector Pin Assignments     39       3.4.3     J4 DIP Connector Pin Assignments     40       3.4.4     Target MONO8 Interface Connector J5 Pin Assignments     41       3.4.5     Power Connector (P1)     42       3.4.5     Power Connector (P1)     42       3.5     Parts List     44       3.6     JBICS Board Layout and Schematic Diagrams     46       Section 4. Using the MON08 Interface       4.1     Introduction     49       4.2     Target System Header Placement and Layout     49       4.2     Target System Header Placement and Layout     49       4.3     Connecting to the In-Circuit Simulator     50       Appendix A. S-Record Information     51       A.2     S-Record Creation     53 |               | 3.2                                                                                                             | MCU Subsystem                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.5       Parts List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | 3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.6 | ICS08JB Board28Clock Selection29Board Reset29Device Configuration Selection30Level Translation30Host System Connector31USB Interface31JBICS Connector Signal Definitions32Target Flex Cable Interface Connectors J1 and J232J3 DIP Connector Pin Assignments39J4 DIP Connector Pin Assignments40Target MONO8 Interface Connector J5 Pin Assignments41Host Computer - JBICS Interconnection (P2)42 |

| Section 4. Using the MON08 Interface         4.1 Introduction.       49         4.2 Target System Header Placement and Layout       49         4.3 Connecting to the In-Circuit Simulator       50         Appendix A. S-Record Information         A.1 Introduction.       51         A.2 S-Record Contents       51         A.3 S-Record Types.       52         A.4 S Record Creation.       53         A.5 S-Record Example       53         A.5.1 S0 Header Record       54         A.5.2 First S1 Record       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                   |

| Section 4. Using the MON08 Interface         4.1       Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.1       Introduction.       49         4.2       Target System Header Placement and Layout       49         4.3       Connecting to the In-Circuit Simulator       50         Appendix A. S-Record Information         A.1       Introduction.       51         A.2       S-Record Contents       51         A.3       S-Record Types.       52         A.4       S Record Creation.       53         A.5       S-Record Example       53         A.5.1       S0 Header Record       54         A.5.2       First S1 Record       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               | 5.0                                                                                                             | Three board Layout and Schematic Diagrams                                                                                                                                                                                                                                                                                                                                                         |

| 4.2       Target System Header Placement and Layout       .49         4.3       Connecting to the In-Circuit Simulator       .50         Appendix A. S-Record Information         A.1       Introduction       .51         A.2       S-Record Contents       .51         A.3       S-Record Types       .52         A.4       S Record Creation       .53         A.5       S-Record Example       .53         A.5.1       S0 Header Record       .54         A.5.2       First S1 Record       .54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                                                                                                 | Section 4. Using the MON08 Interface                                                                                                                                                                                                                                                                                                                                                              |

| Appendix A. S-Record Information         A.1 Introduction.       51         A.2 S-Record Contents       51         A.3 S-Record Types.       52         A.4 S Record Creation.       53         A.5 S-Record Example       53         A.5.1 S0 Header Record       54         A.5.2 First S1 Record       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               | 4.1                                                                                                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                      |

| Appendix A. S-Record Information         A.1 Introduction.       51         A.2 S-Record Contents       51         A.3 S-Record Types.       52         A.4 S Record Creation.       53         A.5 S-Record Example       53         A.5.1 S0 Header Record       54         A.5.2 First S1 Record.       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | 4.2                                                                                                             | Target System Header Placement and Layout                                                                                                                                                                                                                                                                                                                                                         |

| A.1       Introduction.       51         A.2       S-Record Contents       51         A.3       S-Record Types.       52         A.4       S Record Creation.       53         A.5       S-Record Example       53         A.5.1       S0 Header Record       54         A.5.2       First S1 Record.       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | 4.3                                                                                                             | Connecting to the In-Circuit Simulator                                                                                                                                                                                                                                                                                                                                                            |

| A.2       S-Record Contents       51         A.3       S-Record Types       52         A.4       S Record Creation       53         A.5       S-Record Example       53         A.5.1       S0 Header Record       54         A.5.2       First S1 Record       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                                                                                                                 | Appendix A. S-Record Information                                                                                                                                                                                                                                                                                                                                                                  |

| A.3       S-Record Types.       52         A.4       S Record Creation.       53         A.5       S-Record Example       53         A.5.1       S0 Header Record       54         A.5.2       First S1 Record.       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               | A.1                                                                                                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                      |

| A.4 S Record Creation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               | A.2                                                                                                             | S-Record Contents                                                                                                                                                                                                                                                                                                                                                                                 |

| A.5       S-Record Example       53         A.5.1       S0 Header Record       54         A.5.2       First S1 Record       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | A.3                                                                                                             | S-Record Types                                                                                                                                                                                                                                                                                                                                                                                    |

| A.5.1 S0 Header Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               | A.4                                                                                                             | S Record Creation                                                                                                                                                                                                                                                                                                                                                                                 |

| User's Manual M68ICS08JB In-Circuit Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | A.5.1                                                                                                           | S0 Header Record54                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | User's Manual |                                                                                                                 | M68ICS08JB In-Circuit Simulator                                                                                                                                                                                                                                                                                                                                                                   |

| A.5.3 | S9 Termination Record                       |       |

|-------|---------------------------------------------|-------|

| A.5.4 | ASCII Characters                            | 56    |

| Арр   | endix B. Quick Start Hardware Configuration | Guide |

| B.1   | Introduction                                | 57    |

| B.1.1 | JBICS Configurable Jumper Headers           | 58    |

| B.1.2 | Target Interface Cable Connections          | 58    |

| B.2   | Installing the Hardware                     | 59    |

| B.3   | Connecting to a Target System               | 59    |

| B.4   | Installing the Software                     | 60    |

# **Glossary**

# Index

5

# **Table of Contents**

# User's Manual — M68ICS08JB In-Circuit Simulator

# **List of Figures**

| Table | Figure                                    | Page |

|-------|-------------------------------------------|------|

| 1-1   | M68ICS08JB In-Circuit Simulator Board     | 10   |

| 2-1   | P2 Host Computer to JBICS Interconnection | 21   |

| 2-2   | P1 Power Connector                        | 21   |

| 3-1   | P1 Power Connector                        | 40   |

| 3-2   | P2 Host Computer to JBICS Interconnection | 41   |

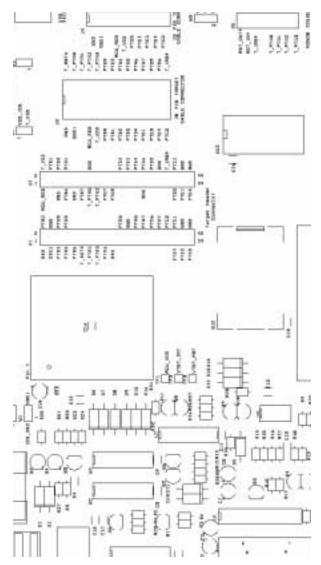

| 3-3   | JBICS Board Layout                        | 44   |

# List of Figures

# User's Manual — M68ICS08JB In-Circuit Simulator

# **List of Tables**

| 1-1  | JBICS Product Components                              | 12 |

|------|-------------------------------------------------------|----|

| 1-2  | Hardware Connector Components                         | 13 |

| 1-3  | Software Components                                   | 14 |

| 1-4  | JBICS Board Specifications                            | 15 |

| 2-1  | JBICS Jumper Header Description                       | 20 |

| 2-2  | Cable/Connector Options for MCUs                      | 21 |

| 3-1  | J1 Target Flex Connector Pin Assignment Descriptions  | 31 |

| 3-2  | J2 Target Flex Connector Pin Assignment Descriptions  | 32 |

| 3-3  | Flex Cable Plug Pin Assignments                       | 34 |

| 3-4  | J3 Connector Pin Assignments                          | 37 |

| 3-5  | J4 Connector Pin Assignments                          | 38 |

| 3-6  | J3 MONO8 Target Connector Pin Assignment Descriptions | 39 |

| 3-7  | Power Connector P1 Pin Assignment Descriptions        | 40 |

| 3-8  | RS-232C Communication Connector P2 Pin Assignments    | 41 |

| 3-9  | USB Connector P4 Pin Assignment Descriptions          | 41 |

| 3-10 | JBICS Parts List                                      | 42 |

| 4-1  | MON08 Target System Connector P1                      | 47 |

| 4-2  | MON08 Target System Connector P2                      | 48 |

| 4-3  | JBICS Jumper Header Description                       | 56 |

| 4-4  | Cable/Connector Options for MCUs                      | 57 |

|      |                                                       |    |

# List of Tables

# **Section 1. General Information**

#### 1.1 Introduction

This section provides general information about the Motorola M68ICS08JB in-circuit simulator (JBICS).

The M68ICS08JB JBICS board is a stand-alone development and debugging tool. It contains the hardware and software needed to develop and simulate source code and to program Motorola's MC68HC908JB8 microcontroller unit (MCU).

The JBICS and it's software form a complete editor, assembler, programmer, simulator, and limited real-time input/output emulator for the MCU. When connection is made between a host PC (personal computer) and target hardware (your prototype product), actual inputs and outputs of the target system may be used during code simulation.

The JBICS can interface with any IBM<sup>®</sup> Windows 95<sup>®</sup>-based computer (or later version) through connection of a single RS-232 serial port using a DB-9 serial cable.

Connection to the target system is accomplished by a ribbon cable, a Motorola M6CLB05C flex cable, a MONO8 cable, or one of two DIP emulation cables (low cost alternatives to the flex cable). The ribbon cable or flex cable or DIP cable is used when an MCU is resident on the JBICS for emulation or simulation, and the MONO8 cable is used to debug or program a target system's MCU, directly, when the MCU resides on the target hardware.

Figure 1-1 M68ICS08JB In-Circuit Simulator Board

The JBICS is a low-cost development system that supports editing, assembling, in-circuit simulation, in-circuit emulation, and FLASH memory programming. Its features include:

- Editing with WinIDE

- Assembling with CASM08Z

- Programming FLASH memory with PROG08SZ

- Simulating in-circuit and stand-alone MC68HC908JB MCUs with ICS08JBZ software, providing:

- Simulation of all instructions, memory, and peripherals

- Simulation of pin inputs from the target system

- Installation of conditional breakpoints, script files, and logfiles

- Debugging and emulation (limited real-time) with ICD08SZ, including:

- Loading code into RAM

User's Manual

M68ICS08JB In-Circuit Simulator

- Executing real-time in RAM or FLASH

- Placing one hardware breakpoint in FLASH

- Placing multiple breakpoints in RAM

- On-line help documentation for all software

- Software integrated into the WinIDE environment, allowing function key access to all applications

- MON08 emulation connection to the target system allowing:

- In-circuit emulation

- In-circuit simulation

- In-circuit programming

- Four modes of operation:

- Standalone using the JBICS as a standalone system without a target board

- Simulation using the JBICS as an in-circuit simulator/emulator with a target cable

- Evaluation using the JBICS for real-time evaluation of the MCU and to debug user developed hardware and software

- Programming using the JBICS as a programmer

- With the ICD08SZ debugging software, code may be run directly out of the MCU's internal FLASH at real-time speeds.

- With the WinIDE, CASM08Z, editor, simulator, and assembler software the function is as a limited real-time emulator.

- With the PROG08SZ software the function is to program MCU FLASH memory.

- With the ICS08JBZ simulation software, the MCU provides the required input/output information that lets the host computer simulate code, performing all functions except for maintaining port values. (The internal FLASH memory on the device is downloaded with a program that generates the appropriate port values.) The ICS08JBZ software on the host computer lets the host computer become a simulator.

- With using the ICD08SZ debugging software, code can be run directly out of the MCU's internal FLASH at real-time speeds.

M68ICS08JB In-Circuit Simulator

• Timing is accomplished through a 6.0 MHz crystal

# 1.2 JBICS Components

The complete JBICS system includes hardware, software, and documentation. **Table 1-1** lists the JBICS product components.

**Table 1-1 JBICS Product Components**

| Part Number      | Description                                                |  |

|------------------|------------------------------------------------------------|--|

| ICS08JB          | JBICS software development package                         |  |

| ICS08JBZ         | JBICS simulator                                            |  |

| ICD08SZ          | JBICS debugger/emulation                                   |  |

| MC68HC908JB8FB   | MCU (44-pin QFP package)                                   |  |

| MC68HC908JB8ADW  | MCU (SOIC Package)                                         |  |

| MC68HC908JB8JP   | MCU (PDIP Package)                                         |  |

| M68CLB05C        | Flex target cable                                          |  |

| KRISTA 22-122    | Serial cable                                               |  |

| FRIWO 11.8999-P5 | Power supply                                               |  |

| M68ICS08JB       | Hardware board                                             |  |

| M68ICS08SOM/D    | M68ICS08JB In-circuit Simulator Software Operator's Manual |  |

| M68ICS08JBHOM/D  | M68ICS08 In-circuit Simulator Hardware Operator's Manual   |  |

#### 1.2.1 JBICS Hardware

Table 1-2 lists the JBICS hardware components.

**Table 1-2. Hardware Connector Components**

| Components | Description                                                                                             |  |

|------------|---------------------------------------------------------------------------------------------------------|--|

| XU1        | Clam shell test socket for Motorola MC68HC908JB8 MCU; 64-pin QFP (quad flat pack)                       |  |

| XU2        | 28-pin SOIC test socket for Motorola MC68HC908JB8 MCU                                                   |  |

| XU3        | 20-pin PDIP test socket for Motorola MC68HC908JB8                                                       |  |

| J1 & J2    | Two 2-row × 20-pin, 0.1-inch spacing connectors to connect JBICS to a target using M68CLB05C flex cable |  |

| J3         | Connector to connect 28-pin DIP emulation cable between JBICS and target.                               |  |

| J4         | Connector to connect 20-pin DIP emulation cable between JBICS and target.                               |  |

| J5         | One 2-row $\times$ 8-pin, 0.1-inch spacing connector to connect to target via MON08 debug circuit.      |  |

| P1         | +5 Vdc input voltage (V <sub>DD</sub> )                                                                 |  |

| P2         | RS-232 to interface JBICS to host computer serial connector (DEKL-9SAT-F)                               |  |

| P3         | Power Terminal                                                                                          |  |

| P4         | USB Series "B" Receptable to interface JBICS to host computer                                           |  |

#### 1.2.2 ICS Interface Software

Windows-optimized software components are referred to, collectively, as the JBICS software (part number ICS08JB). It is a product of *P&E Microcomputer Systems, Inc.*, and is included in the JBICS kit (**Table 1-3**).

**Table 1-3 Software Components**

| Components   | Description                                                                                                              |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------|--|

| WINIDE.EXE   | Integrated development environment (IDE) software interface for editing and performing software or in-circuit simulation |  |

| CASM08Z.EXE  | CASM08Z command-line cross-assembler                                                                                     |  |

| ICSO8SZ.EXE  | In-circuit/stand-alone simulator software for the MC68HC908JB8 MCU                                                       |  |

| PROG08SZ.EXE | FLASH memory programming software                                                                                        |  |

| ICD08SZ.EXE  | In-circuit debugging software for limited, real-time emulation                                                           |  |

# 1.3 Hardware and Software Requirements

The JBICS software requires this minimum hardware and software configuration:

- Windows 95 or later version operating system

- Approximately 2 Mbytes of available random-access memory (RAM) and 5 Mbytes of free disk space

- An RS232 serial port for communications between the JBICS and the host computer

# 1.4 Specifications

Table 1-4 summarizes the JBICS hardware specifications.

**Table 1-4 JBICS Board Specifications**

| Characteristic                 | Specification                       |

|--------------------------------|-------------------------------------|

| Temperature: Operating Storage | 0° to 40°C<br>-40° to +85°C         |

| Relative humidity              | 0 to 95%, non-condensing            |

| Power requirement              | +5 Vdc, from included AC/DC adapter |

### 1.5 About This Manual

The procedural instructions in this manual assume that the user is familiar with the Windows interface and selection procedures.

# 1.6 Customer Support

To obtain information about technical support or ordering parts, call the Motorola help desk at 800-521-6274.

# **Section 2. Preparation and Installation**

#### 2.1 Introduction

This section provides information and instruction for configuring, installing, and readying the M68ICS08JB (JBICS) for use.

# 2.2 Hardware Preparation

This paragraph explains:

- Limitations of the JBICS

- Configuration of the JBICS

- Installation of the JBICS

- Connection of the JBICS to a target system

#### **ESD CAUTION:**

Ordinary amounts of static electricity from clothing or the work environment can damage or degrade electronic devices and equipment. For example, the electronic components installed on the printed circuit board are extremely sensitive to electrostatic discharge (ESD). Wear a grounding wrist strap whenever handling any printed circuit board. This strap provides a conductive path for safely discharging static electricity to ground.

# **Preparation and Installation**

#### 2.2.1 JBICS Limitations

These sub-paragraphs describe system limitations of the JBICS.

#### 2.2.1.1 Port Bit PTA0

Port A0 is used for host to MCU communications, so it is unavailable for emulation.

#### 2.2.1.2 DDRA0

Setting DDRA0, in the Data Direction Register, will stop communications with the simulation or debugger software and will require a system reset to regain communication with the MCU.

#### 2.2.1.3 Port bits PTA1, PTA2, and PTA3

Port bits PTA1, PTA2, and PTA3 are temporarily disconnected from the target system during reset.

#### 2.2.1.4 RST\* signal

RST\* signal is limited because the signal is not a bidirectional, open-drain signal. It is emulated as either an input or output when using the target connectors or as two pins (one input and one output) when using the MONO8 cable.

### 2.2.2 Configuring JBICS Jumper Headers

The JBICS supports four configuration options: standalone, simulation, evaluation, and programming.

- Standalone ICS08JBZ.exe running on the host computer (the JBICS is not connected.) Emulation of the MCU CPU, registers, and I/O ports are done within the host computer environment.

- Simulation Host computer connected to the JBICS via the RS-232 cable and ICS08JBZ.exe running on the host computer. This provides access to the M68HC908JB8 MCU, internal registers, and I/O ports.

User's Manual

M68ICS08JB In-Circuit Simulator

- Evaluation Host computer connected to the JBICS and the JBICS

connected to the target system via the flex cable. This method provides

limited real-time evaluation of the MCU and debugging user developed

hardware and software.

- Programming Host computer connected to the JBICS, and the JBICS connected to the target system via the MON08 cable. Use the PROG08SZ.exe to program the MCU FLASH module. In the programming mode there is limited evaluation (port A0 is used for communications, so it is unavailable for emulation).

Five jumper headers (**Table 2-1**) on the JBICS are used to configure the hardware options.

**Table 2-1 JBICS Jumper Header Description**

| Jumper<br>Header                | Type<br>(Factory<br>Default Shown) | Description                                                                                                                                                                                                                                                                 |  |

|---------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| W1 ICS_OSC or OSC1              | 1 2                                | Jumpers W1 and W4 are configured together for the Oscillator Source.  W1 ON and W4 ON: JBICS MCU and target board clock signals supplied by the JBICS board oscillator Y1.                                                                                                  |  |

| W4<br>OSC1<br>or<br>TGT_OSC1    | 1 2                                | <ul> <li>W1 ON and W4 OFF: JBICS MCU clock signal supplied by oscillator</li> <li>Y1 - Target board has its own clock source.</li> <li>W1 OFF and W4 ON: JBICS MCU clock signal supplied by target board.</li> <li>W1 OFF and W4 OFF: JBICS has no clock source.</li> </ul> |  |

| W2<br>Target<br>System<br>Power | 1 2                                | Jumper: ICS board system power applied to target cable VDD pin.  No Jumper: Allows using a separate power supply for target system.                                                                                                                                         |  |

| W3<br>Reset<br>Source           | 1                                  | Jumper on position 1&2: RST_IN* from target resets on-board ripple counters and MCU.  Jumper on position 2&3: ICS RST_OUT (from RST*) resets target.                                                                                                                        |  |

| W5<br>USB Pull-up<br>Resistor   | 1 0                                | Jumper: Connects 1.5Kohm pull-up resistor from USB D- data line to 3.3V  No Jumper: 1.5K ohm pull-up is disabled and PTE4/D should only be used as I/O Port                                                                                                                 |  |

### 2.2.3 Target Interface Connection Options

There are four ways to connect the JBICS simulator board to your target system:

- Flex cable low-noise target interface connection

- 20- pin DIP Emulation Cable low cost flex cable replacement

- 28- pin DIP Emulation Cable low cost flex cable replacement

- MON08 cable target interface connection with MCU FLASH programming and limited emulation

User's Manual

M68ICS08JB In-Circuit Simulator

Table 2-2 is a quick reference for defining the cable/connector setup to use with the JBICS.

**Table 2-2. Cable/Connector Options for MCUs**

| MCU              | Flex Cable | DIP<br>Emulation<br>Cable | DIP<br>Emulation<br>Cable | MON08<br>Cable |

|------------------|------------|---------------------------|---------------------------|----------------|

| MC68HC90<br>8JB8 | J1 and J2  | J3                        | J4                        | J5             |

### 2.2.4 Host Computer - JBICS Interconnection (P2)

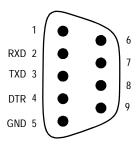

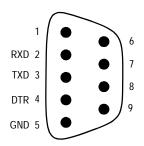

The host computer to JBICS interface is via the single system connector P2, which is a 9-pin, D-type connector (Amp part number AMP-9726-A) (**Figure 2-1**), mounted on the top side of the board.

Connection requires the cable assembly supplied with your JBICS kit, a DB9-male-to-female, 6-ft. (3 m) long serial cable.

Figure 2-1. P2 Host Computer to JBICS Interconnection

#### 2.2.5 Power Connector (P1)

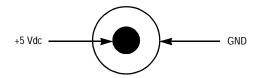

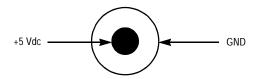

Connect +5-Vdc power directly to the JBICS via connector P1 (**Figure 2-2**) using the provided power supply.

Figure 2-2. P1 Power Connector

M68ICS08JB In-Circuit Simulator

# **Preparation and Installation**

#### 2.2.6 USB Connector

The USB connector is directly connected to the MCU USB interface through the USB data pins (D+ and D-). If the development starts without the target board, the user can connect the USB interface to the host by using a USB standard detachable cable (Series "A" plug to Series "B" plug). In this case, a shunt should be place in the jumper W5 to connect the 1.5Kohm pull-up resistor.

Refer to Section 3, Support Information for pin assignment information.

# 2.3 Connecting the JBICS

The following steps provide instructions for connecting the JBICS to the host PC and power connection.

#### **ESD CAUTION:**

Ordinary amounts of static electricity from clothing or the work environment can damage or degrade electronic devices and equipment. For example, the electronic components installed on the printed circuit board are extremely sensitive to electrostatic discharge (ESD). Wear a grounding wrist strap whenever handling any printed circuit board. This strap provides a conductive path for safely discharging static electricity to ground (common).

- a. Configure the jumpers W-1 through W-5 (Table 2-1) on the JBICS for your application.

- b. Install an MCU into the appropriate socket, for your application, onto the JBICS board.

Note: Observe the pin 1 orientation with the silkscreened dot. The top (label side) of the MCU package must be visible when looking at the component side of the board.

- c. Plug the serial cable into P2 on the JBICS.

- d. Plug the serial cable into the COM port on the host PC.

#### **NOTE:**

Steps e. through g. should not be completed until all connections to the target are completed (*Paragraph 2.4*).

- e. Connect the power cable to P1 on the JBICS board.

- f. Plug the power cable into an ac power outlet, using one of the country-specific adapters.

- g. The JBICS power LED (green) lights.

# 2.4 Connecting the JBICS to the Target System

Connect the JBICS to the target system using one of these methods:

• Emulating using a flex cable for low-noise connection

M68ICS08JB In-Circuit Simulator

### **Preparation and Installation**

When emulating, connect the 80-pin M68CLB05C flex cable to the connectors labeled J1and J2 on the simulator board. Attach the other end of the cable to the appropriate connector on the target system. Target head adapters are available.

• Emulating using a 20-pin DIP emulation cable

When emulating, connect the 20-pin DIP cable to the connector labeled J4 on the simulator board. Attach the other end of the cable to the appropriate connector on the target system. Target head adapters are available.

• Emulating using a 28-pin DIP emulation cable

When emulating, connect the 28-pin DIP cable to the connector labeled J3 on the simulator board. Attach the other end of the cable to the appropriate connector on the target system. Target head adapters are available.

• Using a MON08 cable to debug the target system.

**NOTE:** An MCU must be installed in the target system. No MCU should on the JBICS.

Connect the MON08 debug interface cable to the appropriate MON08 debug interface connector, J5, for communication with the target system's MCU. Attach the other end of the cable to the appropriate connector on the target system.

**NOTE:** For more detailed information on the MON08, refer to Section 4 of this manual.

# 2.5 Installing the Software

For instructions for installing the ICS08 software, refer to *P&E Microcomputer Systems, Inc., M68ICS08HC08 In-Circuit Simulator Operator's Manual,* Motorola document order number M68ICS08SOM/D, and you may refer to http://www.pemicro.com/ics08/index.html#docs.

# **Section 3. Support Information**

#### 3.1 Introduction

This section includes data and information that can be useful in the design, installation, and operation of your application.

## 3.2 MCU Subsystem

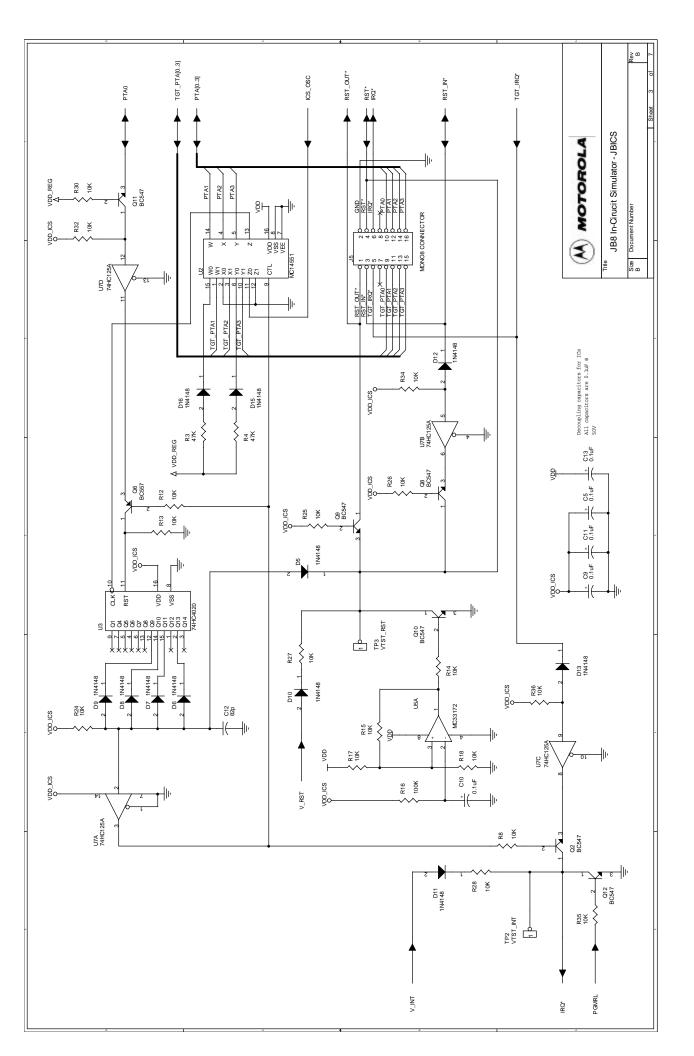

The MCU subsystem consists of the MC68HC908JB8 microcontroller, clock generation and selection, monitor mode control logic that places and holds the JBICS in monitor mode, the bus voltage level translation buffers, and processor operating voltage variable regulator.

The on-board MCU (the test MCU) simulates and debugs the MCU's interface to its peripherals and to other devices on the target board through a variety of connections.

Depending on the connection, the MCU is used in one of three operating modes:

- In the JBICS socket for simple simulation

- In the JBICS socket for programming

- In the JBICS socket connected to the target for emulation

- In the target for MON08 debug operation

# 3.3 JBICS Functional Description

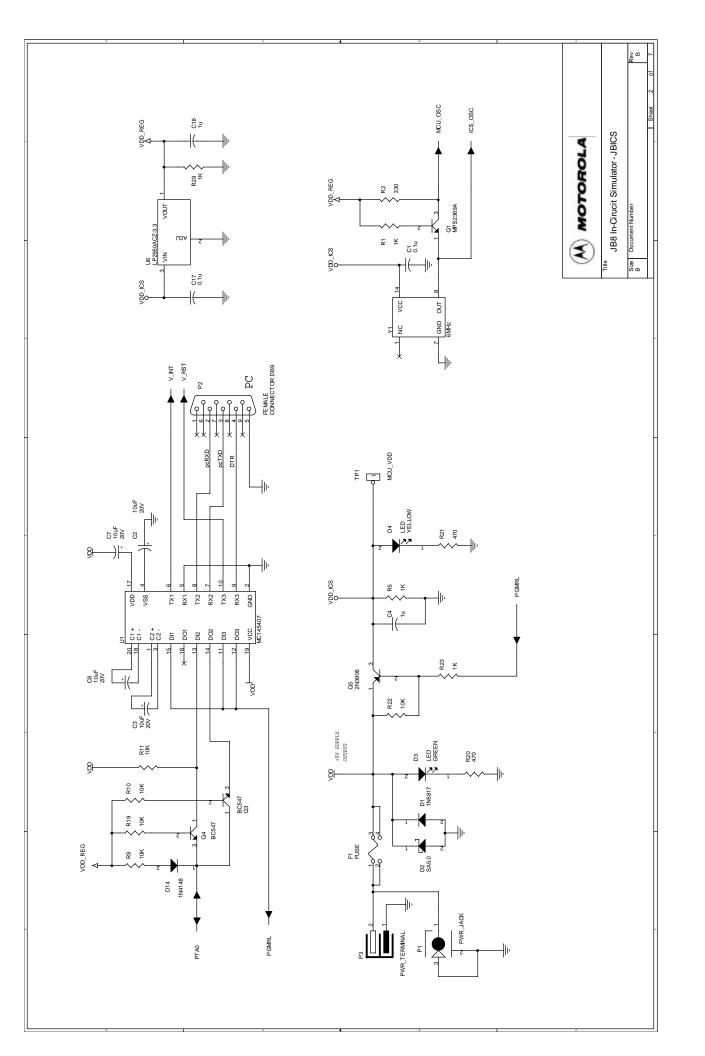

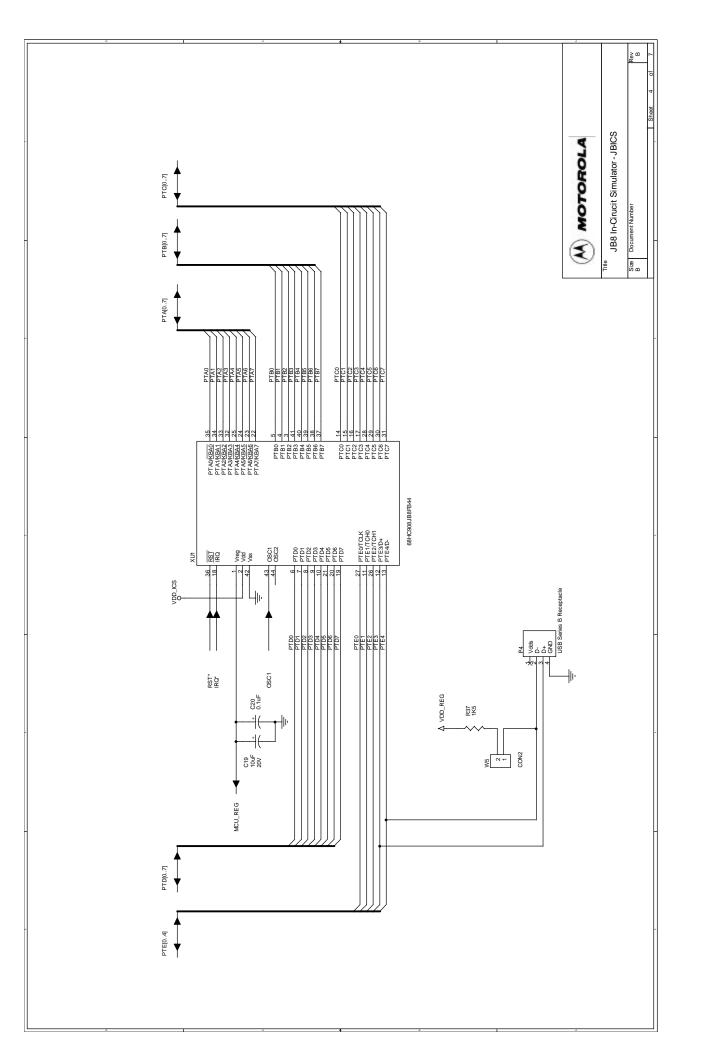

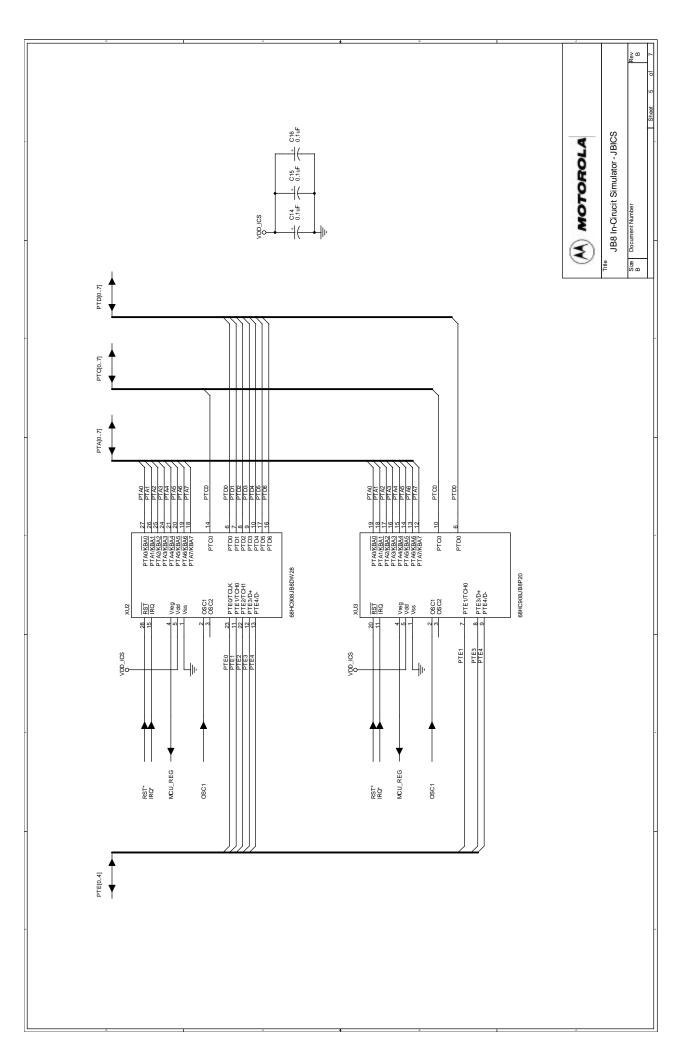

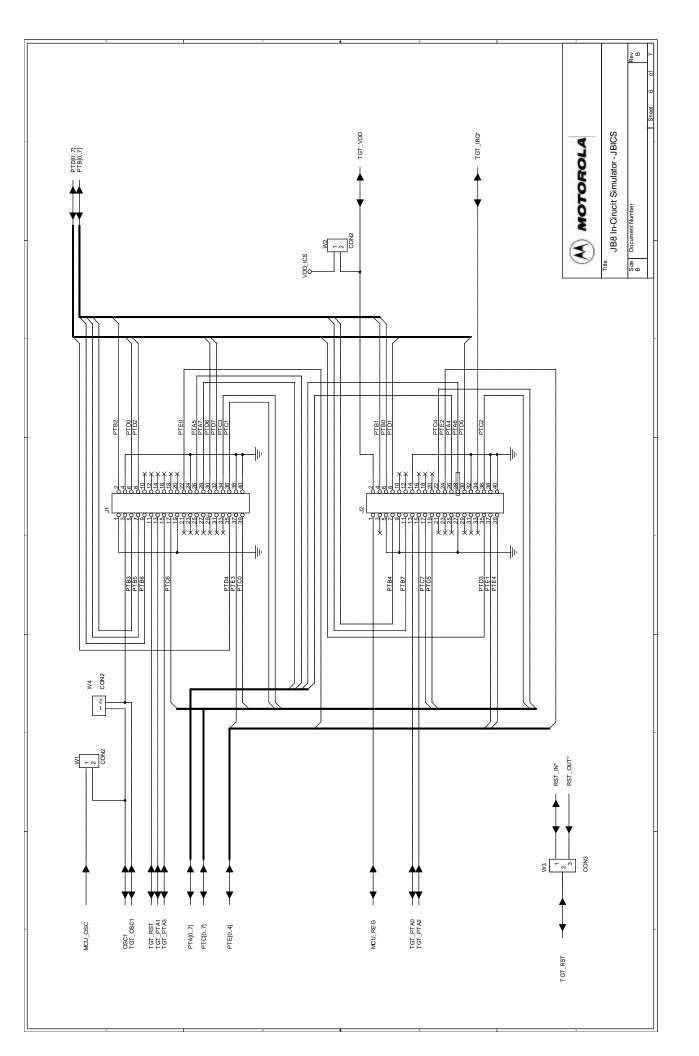

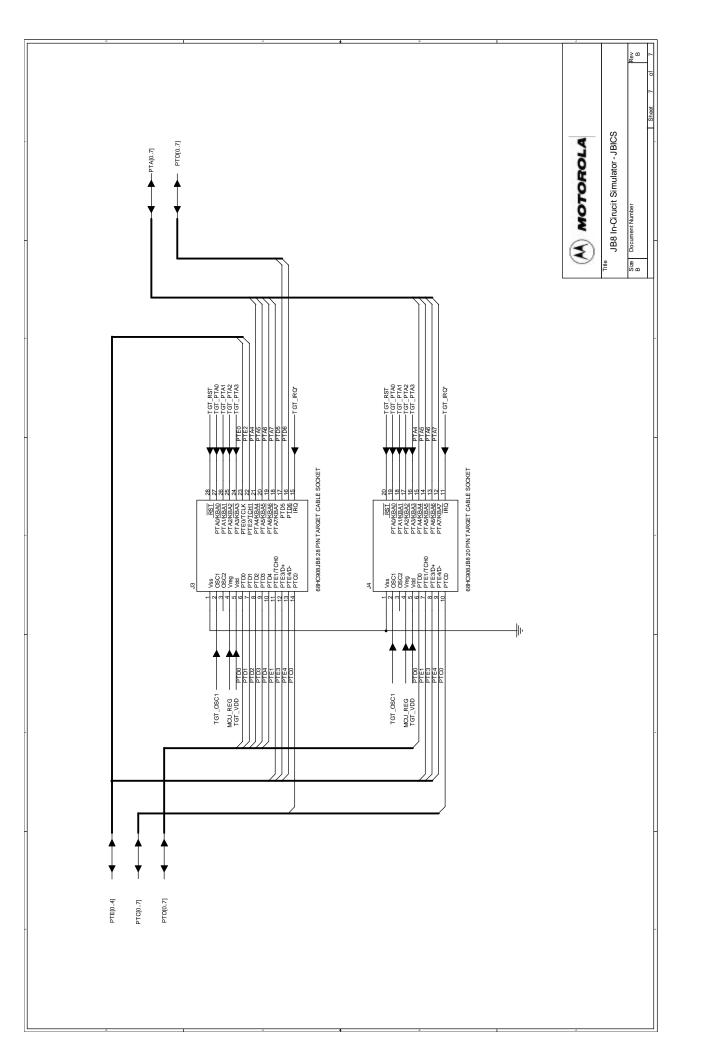

**NOTE:** For the following discussion on the theory of operation of the JBICS, refer to the schematic diagrams in Paragraph 3.6, Figures 3-2 to 3-9 of this section.

#### 3.3.1 ICS08JB Board

The core component of the board is the MC68HC908JB8 MCU (Figure 3-5). This MCU resides either on the ICS08JB board or on a target system.

When the MCU resides on the JBICS, the board may be used as an in-circuit emulator or simulator for the MC68HC908JB8. For this configuration, a target cable is run from the board to the target system.

The JBICS supports three kinds of target cables:

A 20-pin ribbon cable (Figure 3-8) terminated in 20-pin male DIP (Dual In-line Package) headers

A 28-pin ribbon cable (Figure 3-8) terminated in 28-pin male DIP headers

A flexible target head adapter cable (Figure 3-7) (Motorola part number M68CBL05C), terminating in connectors for target head adapter. For a 44-pin QFP-package MCU on the target system, use Motorola THA model number M68TC08JBFB44.

Using a target cable is recommended but optional; the board may be utilized with flying leads to other circuits. The MCU may be any one of the MC68HC908JB8FB, MC68HC908JB8DW, or MC68HC908JB8JP MCUs. On the JBICS board, socket XU1 supports the 44-pin QFP package, socket XU2 supports the 28-pin SOIC package, and socket XU3 supports the 20-pin DIP package.

When the MCU resides on a target system, the ICS08JB board can communicate with the MCU over a 16-pin MON08 cable. The MON08 interface is intended for in-system debugging and programming of an MCU in the target system.

The ICS08JBZ simulation software simulates the operation of an MCU in the PC while communicating with an external MCU to provide I/O functions. The PC executes code simulating the MCU, then sends or requests MCU port data, allowing for a real- world interface for the in-circuit simulator. The simulated MCU operation is much slower than the actual MCU performance, but the simulator allows the actual processing steps to seen and followed, while sill allowing the MCU to interface to all necessary signals within the target system.

The PROG08SZ programming software is used to program the FLASH memory on an MCU. Only one part may be programmed at a time. The MCU to be programmed may be socketed on the JBICS, or it may reside on a target board that sypports MON08.

The JBICS board also provides +5 Vdc power, +8 Vdc power for the VTST\_INT and VTST\_RST voltage required to enter monitor mode, a 6MHz clock signal, and host PC RS-232 level translation.

When using the ICD08SZ debugging software, your code can be run directly out of the MCU's internal FLASH at real-time speeds.

#### 3.3.2 Clock Selection

The JBICS contains a 6-MHz crystal oscillator (Figure 3-3). When the remote target connection is made, the user may opt to feed the output from the JBICS crystal (MCU\_OSC) to the external clock input (OSC1) of the JBICS via W4, a 2-pin shunt (Figure 3-7).

#### 3.3.3 Board Reset

The JBICS includes two reset sources:

- An output from the Power-On Reset (POR) circuit via the host system software

- An internal reset operation of the processor

The host system resets the JBICS (Figure 3-14) by cycling power to most of the ICS circuitry, including the POR circuit; RS-232 handshake line DTR is used for this purpose.

The RESET function of the JBICS is both an input and an output. The JBICS drives its RESET pin low after encountering several different exception conditions. W3 (Figure 2-7) is provided to allow you to select whether the target system can reset the MCU on the JBICS (jumper between pins 1 and 2) or whether the target system receives a reset signal from the JBICS (jumper between pins 2 and 3).

# **Support Information**

RST\* is not a bidirectional, open-drain signal at the target connectors. Removing the jumper leaves the RST-IN\* signal pulled up to MCU operating voltage.

#### 3.3.4 Device Configuration Selection

The operation mode of the JBICS processor is selected at the rising edge of the RESET signal. The JBICS requires that the processor operate in monitor mode. To set monitor mode operation, the IRQ\* line to the JBICS is level shifted to apply  $V_{HI}$  to the processor on the rising edge of reset.  $V_{HI}$  is a signal name that is specified as minimum  $V_{DD}$  +2.5 V and maximum 8.5V, with the highest  $V_{DD}$  of 5V, which gives a range of minimum 7.5V and maximum 8.5V.

The JBICS RST\* pin is the main mode select input and is pulled to logic 0, then logic 1 (processor  $V_{DD}$ ), to select MCU monitor mode. The host software must communicate security bytes to the MCU to resume execution out of reset. Communication to the monitor ROM is via standard, non-return-to-zero (NRZ) mark/space data format on PTA0. The MCU maintains monitor mode and disables the COP module through continued application of  $V_{HI}$  on either IRQ\* or RST\*.

Six commands may be issued by the host software in control of the MCU in monitor mode: read, write, iread, iwrite, readsp, and run. Each command is echoed back through PTA0 for error checking. These commands are described in the M68ICS08JB IN-circuit Simulator Software Operator's Manual.

#### 3.3.5 Level Translation

The JBICS has two operation voltage +3.3 and +5.0 volts while the host development system interface is an RS-232 (com) port. U1 (Figure 3-3) on the ICS converts 5 V logic signals to RS-232 levels. U6 on the ICS converts the 5V to 3.3V. Some transistors are used to translate 5 V logic levels to the MCU operating voltage (3.3V).

#### 3.3.6 Host System Connector

The host system interface is via a 9-pin DB-9 serial connection plug, P2, DEKL-9SAT-F.

#### 3.3.7 USB Interface

A USB series B receptacle, P4, (Figure 3-5) is built in the JBICS board. It can connect to the USB host by USB standard detachable cable (Series "A" plug to Series "B" plug)

### 3.4 JBICS Connector Signal Definitions

The tables in this section describe the pin assignments for the connectors on the JBICS board.

### 3.4.1 Target Flex Cable Interface Connectors J1 and J2

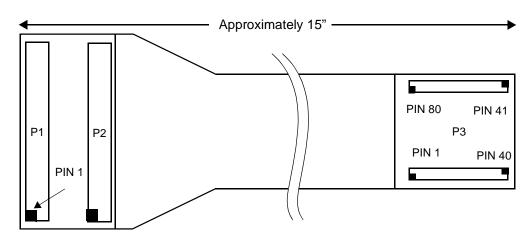

A generic cable (Motorola part number M68CLB05C) connects between the ICS module and target adapter(s) for the different user package targets.

The FLEX cable has two  $2 \times 40$ , 0.1-inch center connector (P1, P2) at the end, which connects to the ICS module. At the opposite end, it has two  $2 \times 20$ , 0.5-inch center connector (P3), which connects to the target adapter.

Figure 0-1. FLEX Cable

**Table 3-1 J1 Target Flex Connector Pin Assignment Descriptions**

| Pin<br>No. | Schematic | Direction     | Signal Description                                          |

|------------|-----------|---------------|-------------------------------------------------------------|

| 1          | GND       |               |                                                             |

| 2          | PTB2      | Bidirectional | General Purpose I/O                                         |

| 3          | TGT_OSC1  | Bidirectional | Clock Signal - JBICS W4 jumper settings determine direction |

| 4          | GND       |               |                                                             |

| 5          | PTB3      | Bidirectional | General Purpose I/O                                         |

| 6          | PTD0      | Bidirectional | General Purpose I/O                                         |

| 7          | PTB5      | Bidirectional | General Purpose I/O                                         |

| 8          | PTD2      | Bidirectional | General Purpose I/O                                         |

| 9          | PTB6      | Bidirectional | General Purpose I/O                                         |

| 10         | N/C       |               |                                                             |

| 11         | TGT_RST   | Bidirectional | Logical-level reset - W3 determines direction               |

| 12         | N/C       |               |                                                             |

| 13         | TGT_PTA1  | Bidirectional | General Purpose I/O                                         |

| 14         | N/C       |               |                                                             |

| 15         | TGT_PTA3  | Bidirectional | General Purpose I/O                                         |

| 16         | N/C       |               |                                                             |

| 17         | PTC6      | Bidirectional | General Purpose I/O                                         |

| 18         | N/C       |               |                                                             |

| 19         | GND       |               |                                                             |

| 20         | N/C       |               |                                                             |

| 21         | N/C       |               |                                                             |

| 22         | PTE0      | Bidirectional | General Purpose I/O                                         |

| 23         | N/C       |               |                                                             |

| 24         | GND       |               |                                                             |

| 25         | N/C       |               |                                                             |

| 26         | PTA5      | Bidirectional | General Purpose I/O                                         |

| 27         | N/C       |               |                                                             |

M68ICS08JB In-Circuit Simulator

| Pin<br>No. | Schematic | Direction     | Signal Description  |

|------------|-----------|---------------|---------------------|

| 28         | PTA7      | Bidirectional | General Purpose I/O |

| 29         | N/C       |               |                     |

| 30         | PTD6      | Bidirectional | General Purpose I/O |

| 31         | N/C       |               |                     |

| 32         | PTD7      | Bidirectional | General Purpose I/O |

| 33         | N/C       |               |                     |

| 34         | PTC3      | Bidirectional | General Purpose I/O |

| 35         | PTD4      | Bidirectional | General Purpose I/O |

| 36         | PTC1      | Bidirectional | General Purpose I/O |

| 37         | PTE3      | Bidirectional | General Purpose I/O |

| 38         | GND       |               |                     |

| 39         | PTC0      | Bidirectional | General Purpose I/O |

| 40         | GND       |               |                     |

**Table 3-2 J2 Target Flex Connector Pin Assignment Descriptions**

| Pin<br>No. | Schematic | Direction     | Signal Description                                                 |  |

|------------|-----------|---------------|--------------------------------------------------------------------|--|

| 1          | MCU-REG   | Out           | 3.3V output of on-chip voltage regulator                           |  |

| 2          | TGT-VDD   | I/O           | 5V JBICS W2 jumper settings determine if signal is input or output |  |

| 3          | N/C       |               |                                                                    |  |

| 4          | PTB1      | Bidirectional | General Purpose I/O                                                |  |

| 5          | GND       |               |                                                                    |  |

| 6          | PTB0      | Bidirectional | General Purpose I/O                                                |  |

| 7          | PTB4      | Bidirectional | General Purpose I/O                                                |  |

| 8          | PTD1      | Bidirectional | General Purpose I/O                                                |  |

| 9          | GND       |               |                                                                    |  |

| 10         | N/C       |               |                                                                    |  |

| 11         | PTB7      | Bidirectional | General Purpose I/O                                                |  |

| 12         | N/C       |               |                                                                    |  |

User's Manual

M68ICS08JB In-Circuit Simulator

| Pin<br>No. | Schematic | Direction     | Signal Description            |  |

|------------|-----------|---------------|-------------------------------|--|

| 13         | TGT-PTA0  | Bidirectional | General Purpose I/O           |  |

| 14         | GND       |               |                               |  |

| 15         | TGT_PTA2  | Bidirectional | General Purpose I/O           |  |

| 16         | N/C       |               |                               |  |

| 17         | PTC7      | Bidirectional | General Purpose I/O           |  |

| 18         | N/C       |               |                               |  |

| 19         | PTC5      | Bidirectional | General Purpose I/O           |  |

| 20         | N/C       |               |                               |  |

| 21         | N/C       |               |                               |  |

| 22         | PTC4      | Bidirectional | General Purpose I/O           |  |

| 23         | N/C       |               |                               |  |

| 24         | PTE2      | Bidirectional | General Purpose I/O           |  |

| 25         | N/C       |               |                               |  |

| 26         | PTA4      | Bidirectional | General Purpose I/O           |  |

| 27         | GND       |               |                               |  |

| 28         | PTA6      | Bidirectional | General Purpose I/O           |  |

| 29         | N/C       |               |                               |  |

| 30         | PTD5      | Bidirectional | General Purpose I/O           |  |

| 31         | N/C       |               |                               |  |

| 32         | GND       |               |                               |  |

| 33         | N/C       |               |                               |  |

| 34         | TGT_IRQ*  | In            | Interrupt Request from Target |  |

| 35         | PTD3      | Bidirectional | General Purpose I/O           |  |

| 36         | PTC2      | Bidirectional | General Purpose I/O           |  |

| 37         | PTE1      | Bidirectional | General Purpose I/O           |  |

| 38         | GND       |               |                               |  |

| 39         | PTE4      | Bidirectional | General Purpose I/O           |  |

| 40         | GND       |               |                               |  |

M68ICS08JB In-Circuit Simulator

**Table 3-3 Flex Cable Plug Pin Assignments**

| Signal   | ICS08JB8<br>Connector P1 Pin<br>Number | ICS08JB8<br>Connector P2 Pin<br>Number | Target Head<br>Adapter Pin<br>Number P3 |

|----------|----------------------------------------|----------------------------------------|-----------------------------------------|

| TGT_VDD  | NA                                     | 2                                      | 1                                       |

| MCU_REG  | NA                                     | 1                                      | 2                                       |

| PTB2     | 2                                      | NA                                     | 3                                       |

| GND      | 1                                      | NA                                     | 4                                       |

| PTB1     | NA                                     | 4                                      | 5                                       |

| NC       | NA                                     | 3                                      | 6                                       |

| GND      | 4                                      | NA                                     | 7                                       |

| OSC1     | 3                                      | NA                                     | 8                                       |

| PTB0     | NA                                     | 6                                      | 9                                       |

| GND      | NA                                     | 5                                      | 10                                      |

| PTD0     | 6                                      | NA                                     | 11                                      |

| PTB3     | 5                                      | NA                                     | 12                                      |

| PTD1     | NA                                     | 8                                      | 13                                      |

| PTB4     | NA                                     | 7                                      | 14                                      |

| PTD2     | 8                                      | NA                                     | 15                                      |

| PTB5     | 7                                      | NA                                     | 16                                      |

| NC       | NA                                     | 10                                     | 17                                      |

| GND      | 19                                     | NA                                     | 18                                      |

| NC       | 10                                     | NA                                     | 19                                      |

| PTB6     | 9                                      | NA                                     | 20                                      |

| NC       | NA                                     | 12                                     | 21                                      |

| PTB7     | NA                                     | 11                                     | 22                                      |

| NC       | 12                                     | NA                                     | 23                                      |

| TGT_RST  | 11                                     | NA                                     | 24                                      |

| GND      | 24                                     | NA                                     | 25                                      |

| TGT_PTA0 | NA                                     | 13                                     | 26                                      |

User's Manual

M68ICS08JB In-Circuit Simulator

| Signal   | ICS08JB8<br>Connector P1 Pin<br>Number | ICS08JB8<br>Connector P2 Pin<br>Number | Target Head<br>Adapter Pin<br>Number P3 |

|----------|----------------------------------------|----------------------------------------|-----------------------------------------|

| NC       | 14                                     | NA                                     | 27                                      |

| TGT_PTA1 | 13                                     | NA                                     | 28                                      |

| NC       | NA                                     | 16                                     | 29                                      |

| TGT_PTA2 | NA                                     | 15                                     | 30                                      |

| NC       | 16                                     | NA                                     | 31                                      |