### 3 V/5 V CMOS 0.5 Ω SPDT/2:1 Mux in SC70

### ADG849

#### FEATURES

Ultralow on-resistance: 0.5 Ω typical 0.8 Ω maximum at 5 V supply Excellent audio performance, ultralow distortion: 0.13 Ω typical 0.24 Ω maximum R<sub>ON</sub> flatness High current carrying capability: 400 mA continuous current 600 mA peak current at 5 V Automotive temperature range: -40°C to +125°C Rail-to-rail operation Typical power consumption (<0.01 µW) Pin-compatible upgrade for the ADG749 and ADG779

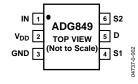

# SUITCHES SHOWN FOR A LOGIC 1 INPUT

FUNCTIONAL BLOCK DIAGRAM

Figure 1.

#### **APPLICATIONS**

Cellular phones PDAs Battery-powered systems Audio and video signal routing Modems PCMCIA cards Hard drives Relay replacement

#### **GENERAL DESCRIPTION**

The ADG849 is a monolithic, CMOS SPDT (single pole, double throw) switch that operates with a supply range of 1.8 V to 5.5 V. It is designed to offer ultralow on-resistance values of typically 0.5  $\Omega$ . This design makes the ADG849 an ideal solution for applications that require minimal distortion through the switch. The ADG849 also has the capability of carrying large amounts of current, typically 600 mA at 5 V operation.

Each switch of the ADG849 conducts equally well in both directions when on. The device exhibits break-before-make switching action, thus preventing momentary shorting when switching channels.

The ADG849 is available in a tiny, 6-lead SC70 package, making it the ideal candidate for space-constrained applications.

#### **PRODUCT HIGHLIGHTS**

- 1. Very low on-resistance,  $0.5 \Omega$  typical.

- 2. Tiny, 6-lead SC70 package.

- 3. Low power dissipation. The CMOS construction ensures low power dissipation.

- 4. High current carrying capability.

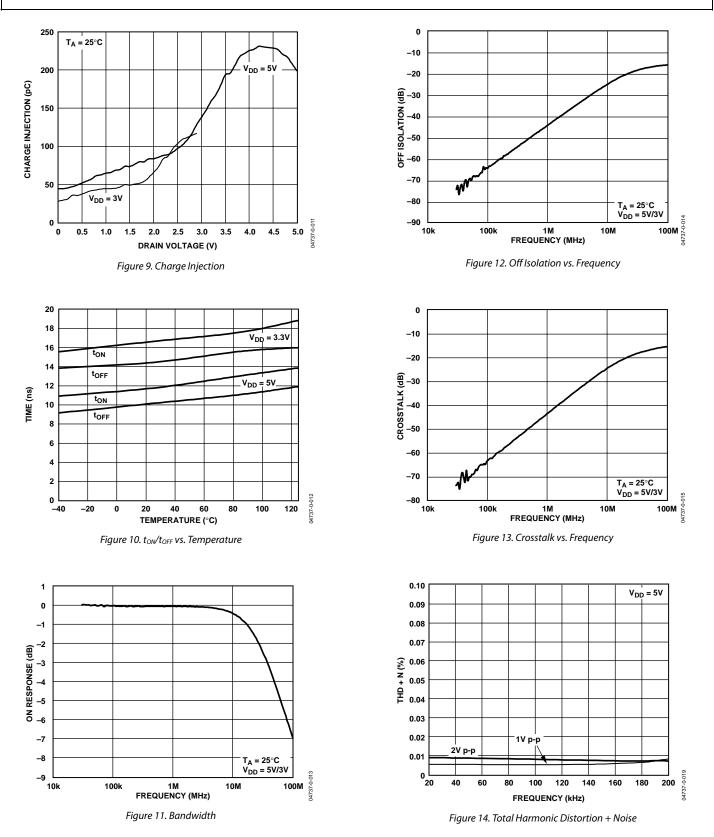

- 5. Low THD + noise (0.01% typ).

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## ADG849\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

#### DOCUMENTATION

#### Data Sheet

- ADG849: 3 V/5 V CMOS 0.5  $\Omega$  SPDT Switch in SC70 Data Sheet

#### **User Guides**

UG-252: Evaluation Board for the AD7280A Lithium Ion Battery Monitoring System

### TOOLS AND SIMULATIONS $\square$

ADG849 SPICE Macro Model

### REFERENCE DESIGNS

• CN0197

#### REFERENCE MATERIALS

#### **Product Selection Guide**

• Switches and Multiplexers Product Selection Guide

#### **Technical Articles**

- CMOS Switches Offer High Performance in Low Power, Wideband Applications

- Data-acquisition system uses fault protection

### DESIGN RESOURCES

- ADG849 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all ADG849 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

### **TABLE OF CONTENTS**

| Specifications                              | 3 |

|---------------------------------------------|---|

| Absolute Maximum Ratings                    | 5 |

| ESD Caution                                 | 5 |

| Pin Configuration and Function Descriptions | 6 |

| 3 | Typical Performance Characteristics7 |

|---|--------------------------------------|

| 5 | Test Circuits9                       |

| 5 | Outline Dimensions 11                |

| 6 | Ordering Guide 11                    |

#### **REVISION HISTORY**

7/04—Revision 0: Initial Version

### **SPECIFICATIONS**

Table 1.  $V_{DD}$  = 4.5 V to 5.5 V, GND = 0 V<sup>1</sup>

| Parameter                                                | +25°C | –40°C to<br>+85°C | –40°C to<br>+125°C       | Unit          | Test Conditions/Comments                                                       |

|----------------------------------------------------------|-------|-------------------|--------------------------|---------------|--------------------------------------------------------------------------------|

| ANALOG SWITCH                                            |       |                   |                          |               |                                                                                |

| Analog Signal Range                                      |       |                   | $0 V$ to $V_{\text{DD}}$ | V             |                                                                                |

| On-Resistance (R <sub>ON</sub> )                         | 0.5   |                   |                          | Ωtyp          | $V_{s} = 0 V \text{ to } V_{DD}$ , $I_{Ds} = -100 \text{ mA}$                  |

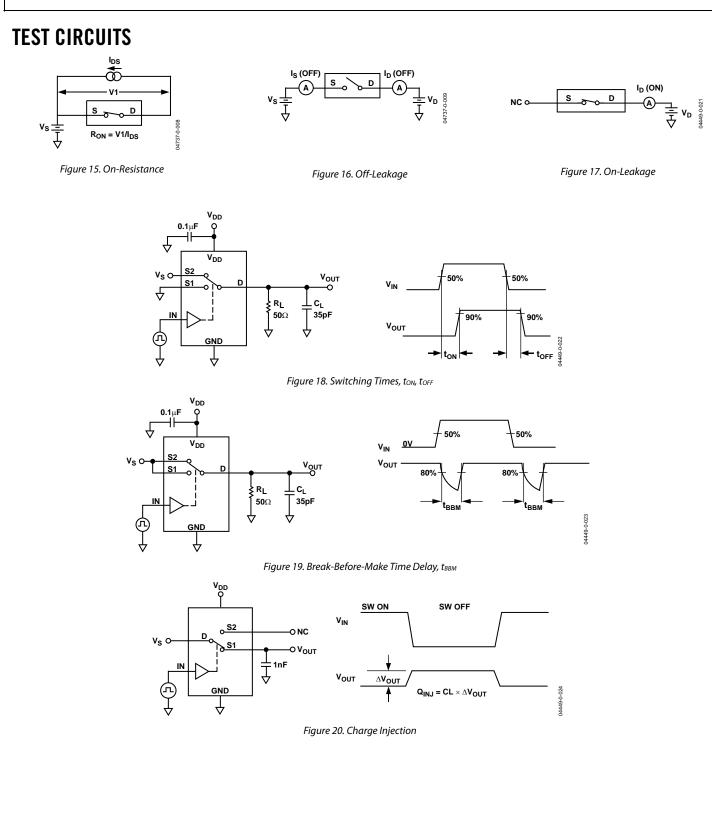

|                                                          | 0.6   | 0.7               | 0.8                      | Ωmax          | See Figure 15                                                                  |

| On-Resistance Match Between Channels $(\Delta R_{ON})$   | 0.05  |                   |                          | Ωtyp          | $V_{\rm S} = 0.85$ V, $I_{\rm DS} = -100$ mA                                   |

|                                                          | 0.095 | 0.11              | 0.125                    | Ωmax          |                                                                                |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> )          | 0.13  |                   |                          | Ωtyp          | $V_{s} = 0 V$ to $V_{DD}$ , $I_{Ds} = -100 \text{ mA}$                         |

|                                                          | 0.18  | 0.22              | 0.24                     | Ωmax          |                                                                                |

| LEAKAGE CURRENTS                                         |       |                   |                          |               | $V_{DD} = 5.5 V$                                                               |

| Source Off Leakage, $I_S$ (Off)                          | ±0.01 |                   |                          | nA typ        | $V_{S} = 4.5 V/1 V$ , $V_{D} = 1 V/4.5 V$ , see Figure 16                      |

| Channel On Leakage, I <sub>D</sub> , I <sub>s</sub> (On) | ±0.04 |                   |                          | nA typ        | $V_{s} = V_{D} = 1 V$ , or $V_{s} = V_{D} = 4.5 V$ ,<br>see Figure 17          |

| DIGITAL INPUTS                                           |       |                   |                          |               |                                                                                |

| Input High Voltage, V <sub>INH</sub>                     |       |                   | 2.0                      | V min         |                                                                                |

| Input Low Voltage, VINL                                  |       |                   | 0.8                      | V max         |                                                                                |

| Input Current                                            |       |                   |                          |               |                                                                                |

| I <sub>INL</sub> or I <sub>INH</sub>                     | 0.005 |                   |                          | μA typ        | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                         |

|                                                          |       |                   | ±0.1                     | μA max        |                                                                                |

| C <sub>IN</sub> , Digital Input Capacitance              | 2.5   |                   |                          | pF typ        |                                                                                |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                     |       |                   |                          |               |                                                                                |

| ton                                                      | 11    |                   |                          | ns typ        | $R_L = 50 \Omega$ , $C_L = 35 pF$                                              |

|                                                          | 15    | 17                | 18                       | ns max        | V <sub>s</sub> = 3 V, see Figure 18                                            |

| toff                                                     | 9     |                   |                          | ns typ        | $R_{L} = 50 \Omega, C_{L} = 35 pF$                                             |

|                                                          | 13    | 14                | 15                       | ns max        | $V_s = 3 V$ , see Figure 18                                                    |

| Break-Before-Make Time Delay, $t_{\text{BBM}}$           | 5     |                   |                          | ns typ        | $R_L = 50 \Omega$ , $C_L = 35 pF$ , $V_{51} = V_{52} = 3 V$ ,<br>see Figure 19 |

|                                                          |       |                   | 1                        | ns min        |                                                                                |

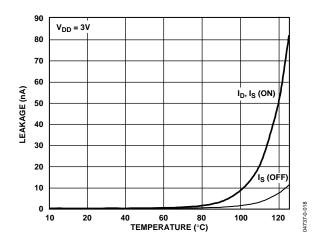

| Charge Injection                                         | 50    |                   |                          | pC typ        | $V_s = 0 V$ , $R_s = 0 \Omega$ , $C_L = 1 nF$ , see Figure 20                  |

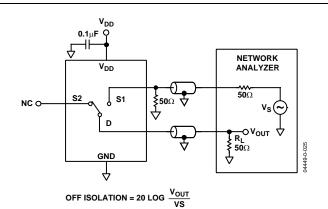

| Off Isolation                                            | -64   |                   |                          | dB typ        | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 100 kHz$<br>see Figure 21              |

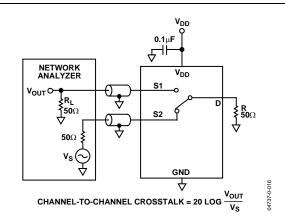

| Channel-to-Channel Crosstalk                             | -64   |                   |                          | dB typ        | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 100 kHz$ ,<br>see Figure 22            |

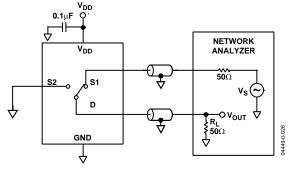

| Bandwidth: –3 dB                                         | 38    |                   |                          | MHz typ       | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 23                               |

| Insertion Loss                                           | 0.04  |                   |                          | dB typ        | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 23                               |

| THD + N                                                  | 0.01  |                   |                          | %             | $R_{L} = 32 \Omega, f = 20 \text{ Hz to } 20 \text{ kHz},$<br>Vs = 2 V p-p     |

| C <sub>s</sub> (Off)                                     | 52    |                   |                          | pF typ        |                                                                                |

| $C_{\rm D}, C_{\rm S}$ (On)                              | 145   |                   |                          | pF typ        |                                                                                |

| POWER REQUIREMENTS                                       | -     |                   |                          | 1° 7°         | $V_{DD} = 5.5 \text{ V}$ , Digital Inputs = 0 V or 5.5 V                       |

| IDD                                                      | 0.001 |                   |                          | μA typ        |                                                                                |

|                                                          |       |                   |                          | 1 m · · · / m |                                                                                |

$^1 The temperature range for the Y version is -40°C to +125°C. <math display="inline">^2$  Guaranteed by design, not subject to production test.

#### Table 2. $V_{DD} = 2.7 \text{ V}$ to 3.6 V, GND = 0 V<sup>1</sup>

| Parameter                                              | +25°C | –40°C to<br>+85°C | –40°C to<br>+125°C | Unit    | Test Conditions/Comments                                                                            |

|--------------------------------------------------------|-------|-------------------|--------------------|---------|-----------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                          |       |                   |                    |         |                                                                                                     |

| Analog Signal Range                                    |       |                   | $0 V to V_{DD}$    | v       |                                                                                                     |

| On-Resistance (R <sub>ON</sub> )                       |       |                   |                    | Ωtyp    | $V_{s} = 0 V \text{ to } V_{DD}$ , $I_{Ds} = -100 \text{ mA}$                                       |

|                                                        | 1.1   | 1.1               | 1.2                | Ωmax    | See Figure 15                                                                                       |

| On-Resistance Match Between Channels $(\Delta R_{ON})$ | 0.05  |                   |                    | Ωtyp    | $V_{\rm S} = 1.5 \text{ V}, I_{\rm DS} = -100 \text{ mA}$                                           |

|                                                        | 0.095 | 0.11              | 0.125              | Ωmax    |                                                                                                     |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> )        | 0.3   |                   |                    | Ωtyp    | $V_{s} = 0 V \text{ to } V_{DD}$ , $I_{Ds} = -100 \text{ mA}$                                       |

| LEAKAGE CURRENTS                                       |       |                   |                    |         | $V_{DD} = 3.6 V$                                                                                    |

| Source Off Leakage, Is (Off)                           | ±0.1  |                   |                    | nA typ  | $V_{s} = 3 V/1 V, V_{D} = 1 V/3 V$ , see Figure 16                                                  |

| Channel On Leakage, $I_D$ , $I_S$ (On)                 | ±0.01 |                   |                    | nA typ  | $V_S = V_D = 1$ V, or $V_S = V_D = 3$ V;<br>see Figure 17                                           |

| DIGITAL INPUTS                                         |       |                   |                    |         |                                                                                                     |

| Input High Voltage, VINH                               |       |                   | 2.0                | V min   |                                                                                                     |

| Input Low Voltage, VINL                                |       |                   | 0.8                | V max   | $V_{DD} = 3 V \text{ to } 3.6 V$                                                                    |

|                                                        |       |                   | 0.7                | V max   | $V_{DD} = 2.7 V$                                                                                    |

| Input Current                                          |       |                   |                    |         |                                                                                                     |

|                                                        | 0.005 |                   |                    | μA typ  | VIN = VINI Or VINH                                                                                  |

|                                                        |       |                   | ±0.1               | µA max  |                                                                                                     |

| C <sub>IN</sub> , Digital Input Capacitance            | 2.5   |                   |                    | pF typ  |                                                                                                     |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                   | 2.0   |                   |                    | P: 17P  |                                                                                                     |

| ton                                                    | 16    |                   |                    | ns typ  | $R_L = 50 \Omega, C_L = 35 pF$                                                                      |

| CON                                                    | 22    | 24                | 26                 | ns max  | $V_s = 1.5 V$ , see Figure 18                                                                       |

| toff                                                   | 13    |                   | 20                 | ns typ  | $R_L = 50 \Omega$ , $C_L = 35 pF$                                                                   |

|                                                        | 18    | 20                | 22                 | ns max  | $V_s = 1.5 V$ , see Figure 18                                                                       |

| Break-Before-Make Time Delay, $t_{\mbox{\tiny BBM}}$   | 7     | 20                |                    | ns typ  | $R_L = 50 \Omega$ , $C_L = 35 pF$ , $V_{S1} = V_{S2} = 1.5 V$ ,<br>see Figure 19                    |

|                                                        |       |                   | 1                  | ns min  |                                                                                                     |

| Charge Injection                                       | 30    |                   |                    | pC typ  | $V_s = 0 V$ , $R_s = 0 \Omega$ , $C_L = 1 nF$ , see Figure 20                                       |

| Off Isolation                                          | -64   |                   |                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 100 kHz$ ,<br>see Figure 21                                 |

| Channel-to-Channel Crosstalk                           | -64   |                   |                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 100 kHz$ ,<br>see Figure 22                                 |

| Bandwidth: –3 dB                                       | 38    |                   |                    | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , see Figure 23                                                    |

| Insertion Loss                                         | 0.04  |                   |                    | dB typ  | $R_L = 50 \Omega C_L = 5 pF$ , see Figure 23                                                        |

| THD + N                                                | 0.02  |                   |                    | %       | $\label{eq:RL} \begin{array}{l} R_{L}=32~\Omega,f=20~Hz~to~20~kHz,\\ Vs=1~V~p\text{-}p \end{array}$ |

| Cs (Off)                                               | 55    |                   |                    | pF typ  | f = 1 MHz                                                                                           |

| C <sub>D</sub> , C <sub>s</sub> (On)                   | 147   |                   |                    | pF typ  | f = 1 MHz                                                                                           |

| POWER REQUIREMENTS                                     |       |                   |                    |         | $V_{DD} = 3.6 V$                                                                                    |

|                                                        |       |                   |                    |         | Digital Inputs = 0 V or 3.6 V                                                                       |

| I <sub>DD</sub>                                        | 0.001 |                   |                    | µA typ  |                                                                                                     |

|                                                        |       |                   | 1.0                | µA max  |                                                                                                     |

$^1 The temperature range for the Y version is -40°C to +125°C. <math display="inline">^2$  Guaranteed by design, not subject to production test.

### **ABSOLUTE MAXIMUM RATINGS**

| Table 3. $T_A = 25^{\circ}C$ , unless otherwise noted |                                                                    |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|

| Parameter                                             | Rating                                                             |  |  |  |  |

| V <sub>DD</sub> to GND                                | –0.3 V to +7 V                                                     |  |  |  |  |

| Analog Inputs <sup>1</sup>                            | -0.3 V to V <sub>DD</sub> + 0.3 V or 30 mA, whichever occurs first |  |  |  |  |

| Digital Inputs                                        | -0.3 V to V <sub>DD</sub> + 0.3 V or 30 mA, whichever occurs first |  |  |  |  |

| Peak Current, S or D                                  | 600 mA (pulsed at 1 ms,<br>10% duty cycle maximum)                 |  |  |  |  |

| Continuous Current, S or D                            | 400 mA                                                             |  |  |  |  |

| Operating Temperature Range                           |                                                                    |  |  |  |  |

| Extended                                              | -40°C to +125°C                                                    |  |  |  |  |

| Storage Temperature Range                             | –65°C to +150°C                                                    |  |  |  |  |

| Junction Temperature                                  | +150°C                                                             |  |  |  |  |

| SC70 Package                                          |                                                                    |  |  |  |  |

| $\theta_{JA}$ Thermal Impedance                       | 332°C/W                                                            |  |  |  |  |

| $\theta_{JC}$ Thermal Impedance                       | 120°C/W                                                            |  |  |  |  |

| Reflow Soldering                                      |                                                                    |  |  |  |  |

| Peak Temperature                                      | 260(0/-5)°C                                                        |  |  |  |  |

| Time at Peak Temperature                              | 10 sec to 40 sec                                                   |  |  |  |  |

| IN | Switch S1 | Switch S2 |

|----|-----------|-----------|

| 0  | On        | Off       |

| 1  | Off       | On        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.

<sup>1</sup> Overvoltages at IN, S, or D will be clamped by internal diodes. Current should be limited to the maximum ratings given.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration

#### Table 5. Terminology

| Mnemonic                             | Function                                                                                                                                         |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>                      | Most Positive Power Supply Potential.                                                                                                            |

| GND                                  | Ground (0 V) Reference.                                                                                                                          |

| IDD                                  | Positive Supply Current.                                                                                                                         |

| S                                    | Source Terminal. May be an input or output.                                                                                                      |

| D                                    | Drain Terminal. May be an input or output.                                                                                                       |

| IN                                   | Logic Control Input.                                                                                                                             |

| Ron                                  | Ohmic Resistance between D and S.                                                                                                                |

| ΔRon                                 | On-Resistance Match Between any Two Channels i.e., Ron Maximum to Ron Minimum.                                                                   |

| R <sub>FLAT</sub> (ON)               | Flatness is defined as the difference between the maximum and minimum value of on resistance as measured over the specified analog signal range. |

| Is (Off)                             | Source Leakage Current with the Switch Off.                                                                                                      |

| I <sub>D</sub> , Is (On)             | Channel Leakage Current with the Switch On.                                                                                                      |

| V <sub>D</sub> (V <sub>S</sub> )     | Analog Voltage on Terminals D, S.                                                                                                                |

| VINL                                 | Maximum Input Voltage for Logic 0.                                                                                                               |

| V <sub>INH</sub>                     | Minimum Input Voltage for Logic 1.                                                                                                               |

| I <sub>INL</sub> (I <sub>INH</sub> ) | Input Current of the Digital Input.                                                                                                              |

| C <sub>s</sub> (Off)                 | Off Switch Source Capacitance. Measured with reference to ground.                                                                                |

| C <sub>D</sub> , C <sub>S</sub> (On) | On Switch Capacitance. Measured with reference to ground.                                                                                        |

| t <sub>on</sub>                      | Delay time between the 50% and 90% points of the digital input and switch on condition.                                                          |

| toff                                 | Delay time between the 50% and 90% points of the digital input and switch off condition.                                                         |

| t <sub>BBM</sub>                     | On or off time measured between the 80% points of both switches when switching from one to another.                                              |

| Charge<br>Injection                  | A measure of the glitch impulse transfered from the digital input to the analog output during switching.                                         |

| Crosstalk                            | A measure of unwanted signal that is coupled through from one channel to another as a result of parasitic capacitance.                           |

| Off Isolation                        | A measure of unwanted signal coupling through an off switch.                                                                                     |

| Bandwidth                            | The frequency at which the output is attenuated by 3 dB.                                                                                         |

| On-Response                          | The frequency response of the on switch.                                                                                                         |

| Insertion Loss                       | The loss due to the on-resistance of the switch.                                                                                                 |

| THD + N                              | The ratio of harmonic amplitudes plus the noise of a signal to the fundamental.                                                                  |

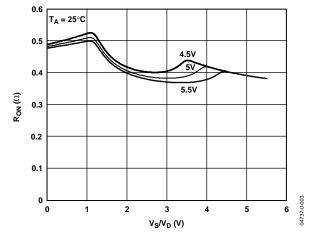

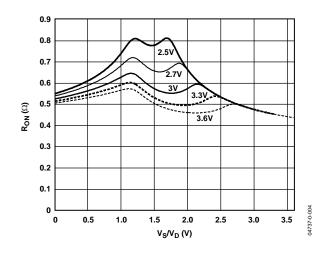

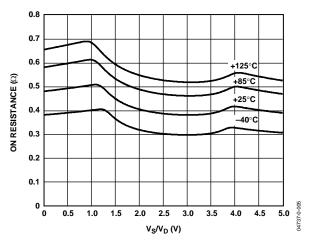

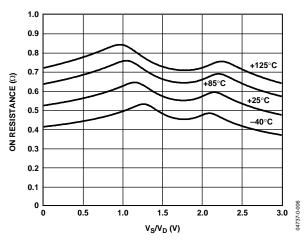

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 3. On-Resistance vs.  $V_D/V_{s}$ ,  $V_{DD} = 5 V \pm 10\%$

Figure 4. On-Resistance vs.  $V_D/V_s$ ,  $V_{DD} = 2.5 V$  to 3.6 V

Figure 5. On-Resistance vs. Temperature,  $V_{DD} = 5 V$

Figure 6. On-Resistance vs. Temperature,  $V_{DD} = 3 V$

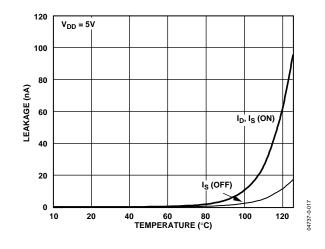

Figure 7. Leakage Currents vs. Temperature,  $V_{DD} = 5 V$

Figure 8. Leakage Currents vs. Temperature,  $V_{DD} = 3 V$

Figure 21. Off Isolation

Figure 22. Channel-to-Channel Crosstalk

INSERTION LOSS = 20 LOG  $\frac{V_{OUT} \text{ WITH SWITCH}}{V_{OUT} \text{ WITHOUT SWITCH}}$

Figure 23. Bandwidth

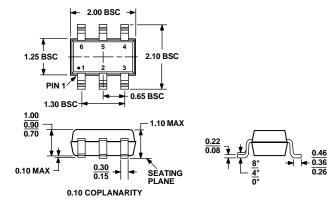

### **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-203AB

Figure 24. 6-Lead SC70 Package [KS-6] Dimensions shown in Millimeters

#### **ORDERING GUIDE**

| Model                          | Temperature Range | Package Description          | Package<br>Option | Branding <sup>1</sup> |

|--------------------------------|-------------------|------------------------------|-------------------|-----------------------|

| ADG849YKSZ-500RL7 <sup>2</sup> | –40°C to +125°C   | SC70 (Plastic Surface Mount) | KS-6              | SNA                   |

| ADG849YKSZ-REEL <sup>2</sup>   | -40°C to +125°C   | SC70 (Plastic Surface Mount) | KS-6              | SNA                   |

| ADG849YKSZ-REEL7 <sup>2</sup>  | –40°C to +125°C   | SC70 (Plastic Surface Mount) | KS-6              | SNA                   |

$^{\rm 1}$  Branding on all packages is limited to three characters due to space constraints.  $^{\rm 2}$  Z = Pb-free part.

### NOTES

www.analog.com

© 2004 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D04737-0-7/04(0)

Rev. 0| Page 12 of 12