# **MCF547x Reference Manual**

Devices Supported:

MCF5475 MCF5472

MCF5474 MCF5471

MCF5473 MCF5470

Document Number: MCF5475RM

Rev. 5

4/2009

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku,

Tokyo 153-0064

Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or +1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The ARM POWERED logo is a registered trademark of ARM Limited. ARM7TDMI-S is a trademark of ARM Limited. Java and all other Java-based marks are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries. The PowerPC name is a trademark of IBM Corp. and is used under license. The described product contains a PowerPC processor core. The PowerPC name is a trademark of IBM Corp. and used under license. The described product is a PowerPC microprocessor. The PowerPC name is a trademark of IBM Corp. and is used under license. The described product is a PowerPC microprocessor core. The PowerPC name is a trademark of IBM Corp. and is used under license. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2008. All rights reserved.

MCF5475RM Rev. 5 4/2009

| Overview                                 | 1  |

|------------------------------------------|----|

| Signal Descriptions                      | 2  |

| ColdFire Core                            | 3  |

| Enhanced Multiply-Accumulate Unit (EMAC) | 4  |

| Memory Management Unit (MMU)             | 5  |

| Floating-Point Unit (FPU)                | 6  |

| Local Memory                             | 7  |

| Debug Support                            | 8  |

| System Integration Unit (SIU)            | 9  |

| Internal Clocks and Bus Architecture     | 10 |

| General Purpose Timers (GPT)             | 11 |

| Slice Timers (SLT)                       | 12 |

| Interrupt Controller (INTC)              | 13 |

| Edge Port Module (EPORT)                 | 14 |

| General Purpose I/O (GPIO)               | 15 |

| System SRAM                              | 16 |

| FlexBus                                  | 17 |

| SDRAM Controller (SDRAMC)                | 18 |

| PCI Bus Controller (PCI)                 | 19 |

| PCI Bus Arbiter (PCIARB)                 | 20 |

| Integrated Secuity Engine (SEC)          | 21 |

| IEEE 1149.1 Test Access Port (JTAG)      | 22 |

| Multichannel DMA (MCD)                   | 23 |

| Comm Bus FIFO Interface                  | 24 |

| Comm Timer Module (CTM)                  | 25 |

| Programmable Serial Controller (PSC)     | 26 |

| DMA Serial Peripheral Interface (DSPI)   | 27 |

| I <sup>2</sup> C interface               | 28 |

| USB 2.0 Device Controller                | 29 |

| Fast Ethernet Controller (FEC)           | 30 |

| Mechanical Data                          | 31 |

|                                          |    |

| Register Memory Map Quick Reference      | A  |

| ·                                        |    |

Index IND

| 1  | Overview                                 |

|----|------------------------------------------|

| 2  | Signal Descriptions                      |

| 3  | ColdFire Core                            |

| 4  | Enhanced Multiply-Accumulate Unit (EMAC) |

| 5  | Memory Management Unit (MMU)             |

| 6  | Floating-Point Unit (FPU)                |

| 7  | Local Memory                             |

| 8  | Debug Support                            |

| 9  | System Integration Unit (SIU)            |

| 10 | Internal Clocks and Bus Architecture     |

| 11 | General Purpose Timers (GPT)             |

| 12 | Slice Timers (SLT)                       |

| 13 | Interrupt Controller (INTC)              |

| 14 | Edge Port Module (EPORT)                 |

| 15 | General Purpose I/O (GPIO)               |

| 16 | System SRAM                              |

| 17 | FlexBus                                  |

| 18 | SDRAM Controller (SDRAMC)                |

| 19 | PCI Bus Controller (PCI)                 |

| 20 | PCI Bus Arbiter (PCIARB)                 |

| 21 | Integrated Secuity Engine (SEC)          |

| 22 | IEEE 1149.1 Test Access Port (JTAG)      |

| 23 | Multichannel DMA (MCD)                   |

| 24 | Comm Bus FIFO Interface                  |

| 25 | Comm Timer Module (CTM)                  |

| 26 | Programmable Serial Controller (PSC)     |

| 27 | DMA Serial Peripheral Interface (DSPI)   |

| 28 | I <sup>2</sup> C interface               |

| 29 | USB 2.0 Device Controller                |

| 30 | Fast Ethernet Controller (FEC)           |

| 31 | Mechanical Data                          |

|    |                                          |

A Register Memory Map Quick Reference IND Index

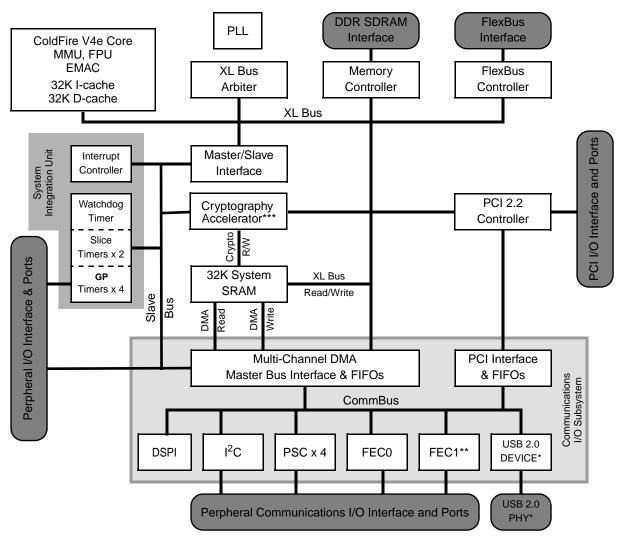

# Chapter 1 Overview

| 1.1 | MCF547    | x Family Overview                              | 1-1  |

|-----|-----------|------------------------------------------------|------|

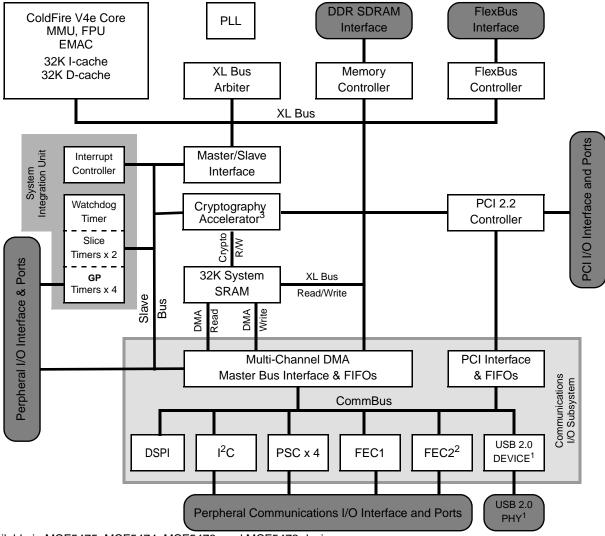

| 1.2 | MCF547    | x Block Diagram                                | 1-2  |

| 1.3 |           | x Family Products                              |      |

| 1.4 | MCF547    | x Family Features                              | 1-3  |

|     | 1.4.1     | ColdFire V4e Core Overview                     | 1-5  |

|     | 1.4.2     | Debug Module (BDM)                             | 1-6  |

|     | 1.4.3     | JTAG                                           | 1-6  |

|     | 1.4.4     | On-Chip Memories                               | 1-7  |

|     | 1.4.5     | PLL and Chip Clocking Options                  | 1-7  |

|     | 1.4.6     | Communications I/O Subsystem                   | 1-8  |

|     | 1.4.7     | DDR SDRAM Memory Controller                    | 1-10 |

|     | 1.4.8     | Peripheral Component Interconnect (PCI)        | 1-10 |

|     | 1.4.9     | Flexible Local Bus (FlexBus)                   | 1-10 |

|     | 1.4.10    | Security Encryption Controller (SEC)           | 1-11 |

|     | 1.4.11    | System Integration Unit (SIU)                  | 1-11 |

|     |           | Chapter 2                                      |      |

|     |           | Signal Descriptions                            |      |

| 2.1 | Introduct | tion                                           | 2-1  |

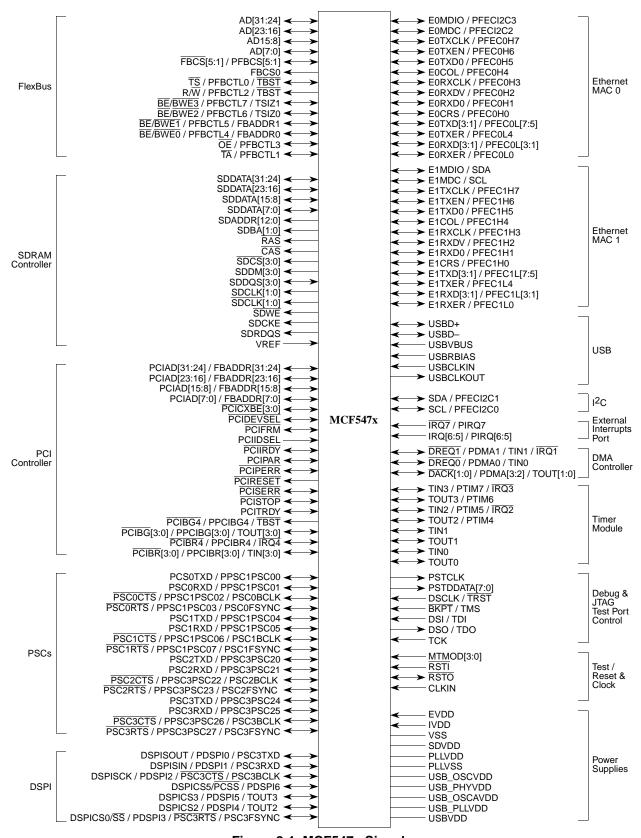

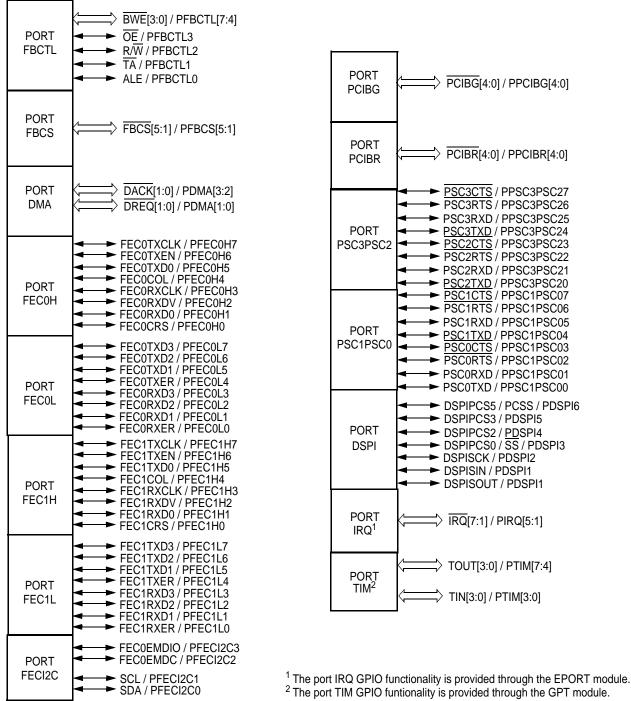

|     | 2.1.1     | Block Diagram                                  | 2-1  |

| 2.2 |           | x External Signals                             |      |

|     | 2.2.1     | FlexBus Signals                                |      |

|     | 2.2.2     | SDRAM Controller Signals                       |      |

|     | 2.2.3     | PCI Controller Signals                         |      |

|     | 2.2.4     | Interrupt Control Signals                      |      |

|     | 2.2.5     | Clock and Reset Signals                        |      |

|     | 2.2.6     | Reset Configuration Pins                       |      |

|     | 2.2.7     | Ethernet Module Signals                        |      |

|     | 2.2.8     | Universal Serial Bus (USB)                     |      |

|     | 2.2.9     | DMA Serial Peripheral Interface (DSPI) Signals |      |

|     | 2.2.10    | I <sup>2</sup> C I/O Signals                   |      |

|     | 2.2.11    | PSC Module Signals                             |      |

|     | 2.2.12    | DMA Controller Module Signals                  |      |

|     | 2.2.13    | Timer Module Signals                           |      |

|     | 2.2.14    | Debug Support Signals                          |      |

|     | 2.2.15    | Test Signals                                   |      |

|     | 2.2.16    | Power and Reference Pins                       | 2-30 |

# Chapter 3 ColdFire Core

| 3.1 | Core Ov       | erview                                        | 3-1  |

|-----|---------------|-----------------------------------------------|------|

| 3.2 | Features      |                                               | 3-1  |

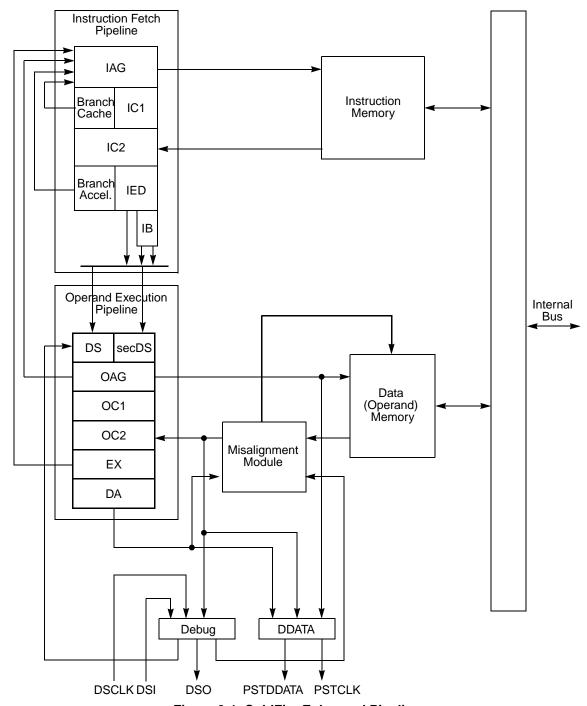

|     | 3.2.1         | Enhanced Pipelines                            | 3-2  |

|     | 3.2.2         | Debug Module Enhancements                     | 3-6  |

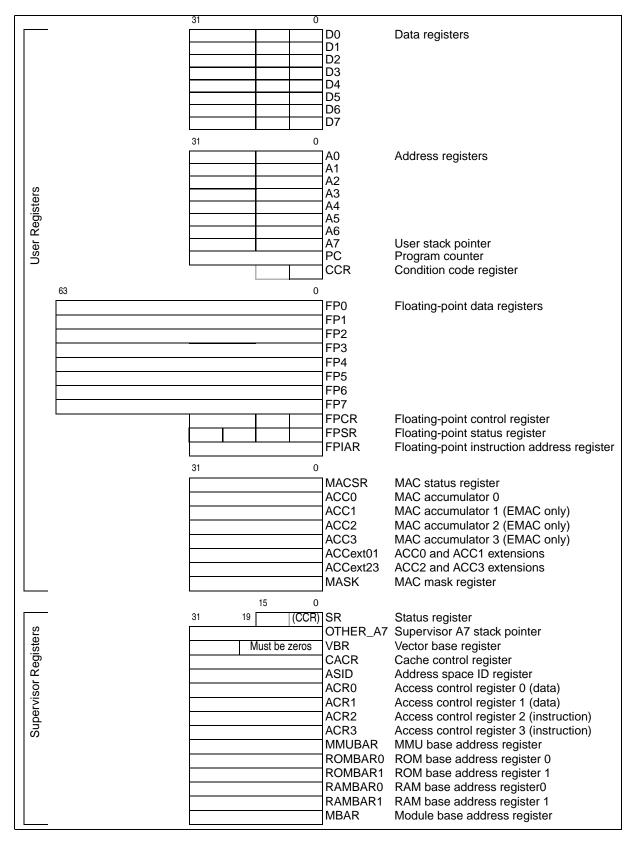

| 3.3 | Program       | ming Model                                    | 3-7  |

|     | 3.3.1         | User Programming Model                        | 3-9  |

|     | 3.3.2         | User Stack Pointer (A7)                       |      |

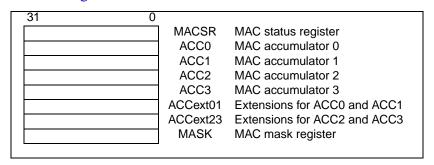

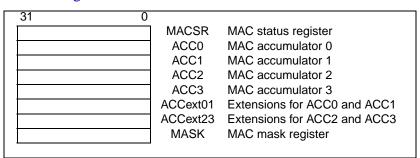

|     | 3.3.3         | EMAC Programming Model                        |      |

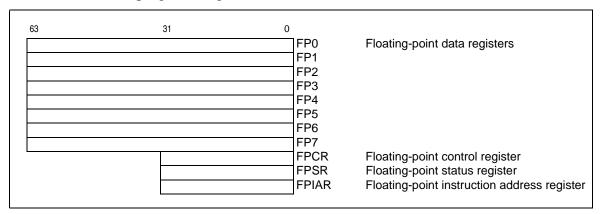

|     | 3.3.4         | FPU Programming Model                         |      |

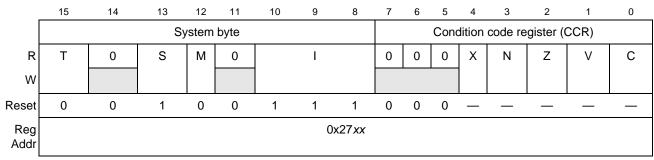

|     | 3.3.5         | Supervisor Programming Model                  |      |

|     | 3.3.6         | Programming Model Table                       |      |

| 3.4 | Data For      | mat Summary                                   |      |

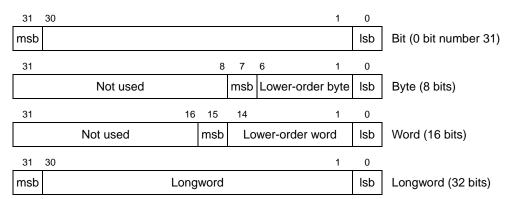

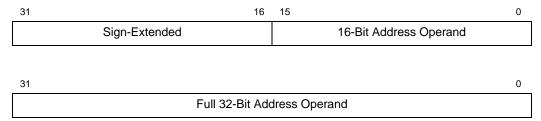

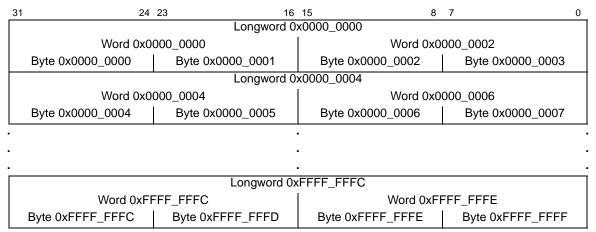

|     | 3.4.1         | Data Organization in Registers                | 3-15 |

|     | 3.4.2         | EMAC Data Representation                      |      |

| 3.5 | Addressi      | ing Mode Summary                              |      |

| 3.6 |               | on Set Summary                                |      |

|     | 3.6.1         | Additions to the Instruction Set Architecture |      |

|     | 3.6.2         | Instruction Set Summary                       |      |

| 3.7 |               | on Execution Timing                           |      |

|     | 3.7.1         | MOVE Instruction Execution Timing             |      |

|     | 3.7.2         | One-Operand Instruction Execution Timing      |      |

|     | 3.7.3         | Two-Operand Instruction Execution Timing      |      |

|     | 3.7.4         | Miscellaneous Instruction Execution Timing    |      |

|     | 3.7.5         | Branch Instruction Execution Timing           |      |

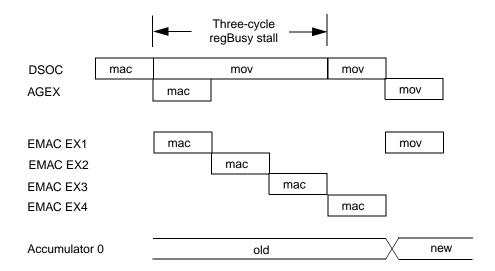

|     | 3.7.6         | EMAC Instruction Execution Times              |      |

|     | 3.7.7         | FPU Instruction Execution Times               |      |

| 3.8 | Exceptio      | on Processing Overview                        |      |

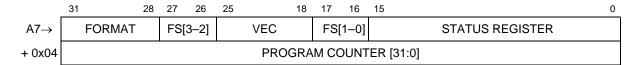

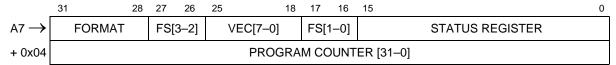

|     | 3.8.1         | Exception Stack Frame Definition              |      |

|     | 3.8.2         | Processor Exceptions                          |      |

| 3.9 | Precise F     | Faults                                        |      |

| 0.5 | 11001501      |                                               |      |

|     |               | Chapter 4                                     |      |

|     |               | Enhanced Multiply-Accumulate Unit (EMAC)      |      |

| 4.1 | Introduc      | • • • • • • • • • • • • • • • • • • • •       | 4-1  |

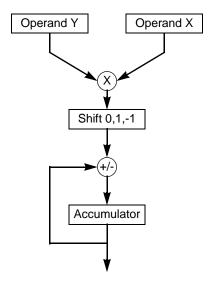

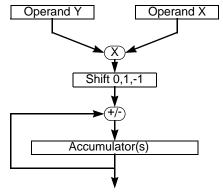

|     | 4.1.1         | MAC Overview                                  |      |

|     | 4.1.2         | General Operation                             |      |

| 4.2 |               | Map/Register Definition                       |      |

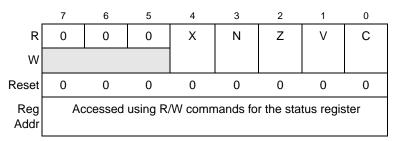

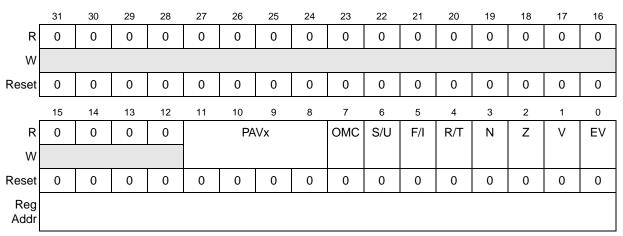

|     | 4.2.1         | MAC Status Register (MACSR)                   |      |

|     | 4.2.2         | Mask Register (MASK)                          |      |

| 4.3 |               | Instruction Set Summary                       |      |

| 1.5 | 4.3.1         | EMAC Instruction Execution Timing             |      |

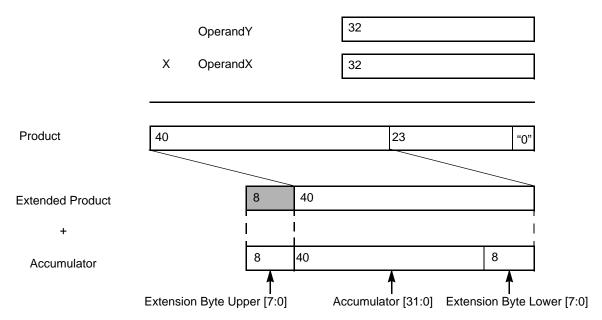

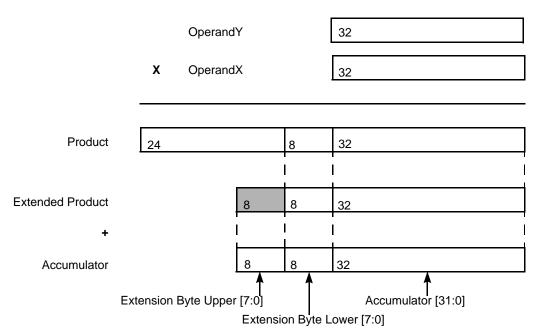

|     | 4.3.2         | Data Representation                           |      |

|     | 4.3.3         | EMAC Opcodes                                  |      |

|     | <b>ਜ.ਹ.</b> ਹ | Diff to Opcodes                               | 4-13 |

# Chapter 5 Memory Management Unit (MMU)

| 5.1        | Features       | S                                                   | 5-1             |

|------------|----------------|-----------------------------------------------------|-----------------|

| 5.2        |                | Memory Management Architecture                      |                 |

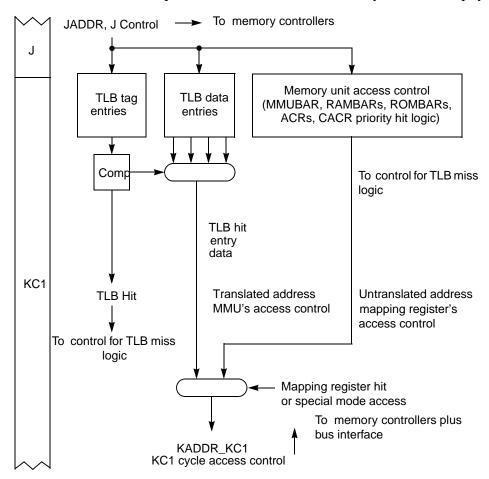

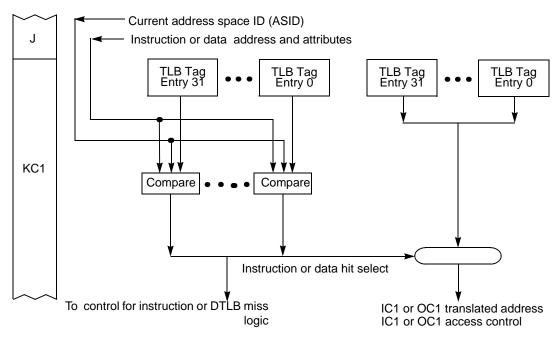

|            | 5.2.1          | MMU Architecture Features                           | 5-1             |

|            | 5.2.2          | MMU Architecture Location                           | 5-2             |

|            | 5.2.3          | MMU Architecture Implementation                     | 5-3             |

| 5.3        | Debugg         | ing in a Virtual Environment                        | 5-7             |

| 5.4        | Virtual 1      | Memory Architecture Processor Support               | 5-7             |

|            | 5.4.1          | Precise Faults                                      |                 |

|            | 5.4.2          | Supervisor/User Stack Pointers                      | 5-7             |

|            | 5.4.3          | Access Error Stack Frame Additions                  | 5-8             |

| 5.5        | MMU D          | Definition                                          | 5-9             |

|            | 5.5.1          | Effective Address Attribute Determination           | 5-9             |

|            | 5.5.2          | MMU Functionality                                   | 5-10            |

|            | 5.5.3          | MMU Organization                                    | 5-10            |

|            | 5.5.4          | MMU TLB                                             | 5-18            |

|            | 5.5.5          | MMU Operation                                       | 5-19            |

| 5.6        | MMU I          | mplementation                                       | 5-20            |

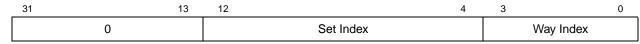

|            | 5.6.1          | TLB Address Fields                                  | 5-20            |

|            | 5.6.2          | TLB Replacement Algorithm                           | 5-21            |

|            | 5.6.3          | TLB Locked Entries                                  | 5-22            |

| 5.7        | MMU I          | nstructions                                         | 5-23            |

|            |                |                                                     |                 |

|            |                | Chapter 6                                           |                 |

| <i>c</i> 1 | Interedise     | Floating-Point Unit (FPU)                           | 6.1             |

| 6.1        |                | Overwiew.                                           |                 |

| <i>(</i> 2 | 6.1.1          | Overview                                            |                 |

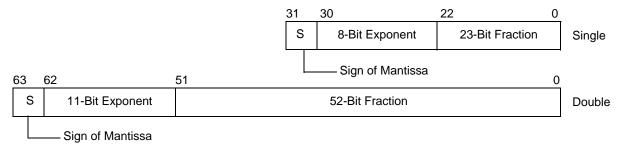

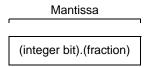

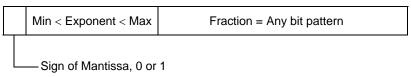

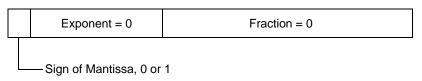

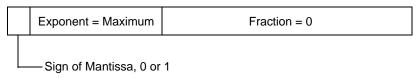

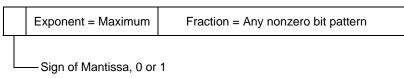

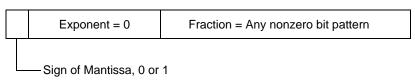

| 6.2        | -              | 1 Data Formats and Types                            |                 |

|            | 6.2.1<br>6.2.2 | Signed-Integer Data Formats                         |                 |

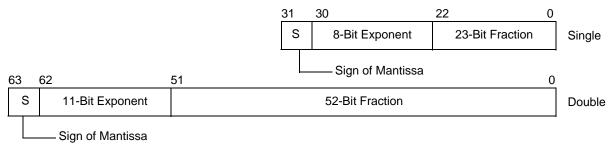

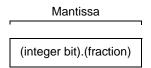

|            |                | Floating-Point Data Formats                         |                 |

| 62         | 6.2.3          | Floating-Point Data Types Definition                |                 |

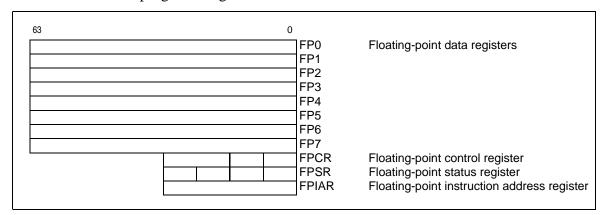

| 6.3        | 6.3.1          | Floating-Point Data Registers (FP0–FP7)             |                 |

|            | 6.3.1          |                                                     |                 |

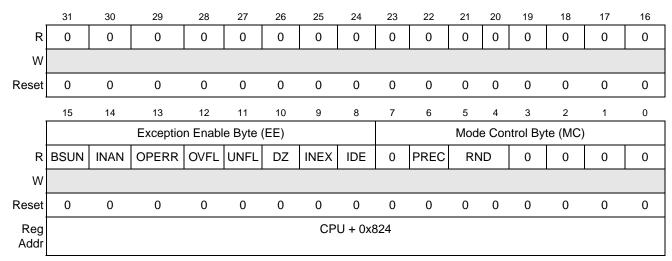

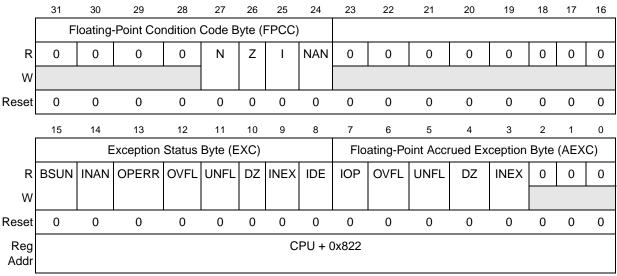

|            | 6.3.3          | Floating-Point Control Register (FPCR)              |                 |

|            | 6.3.4          | Floating Point Instruction Address Register (FPIAR) |                 |

| <i>c</i> 1 |                | Floating-Point Instruction Address Register (FPIAR) |                 |

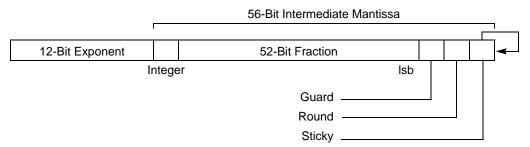

| 6.4        | 6.4.1          | g-Point Computational Accuracy                      |                 |

|            | 6.4.1          | Intermediate Result                                 |                 |

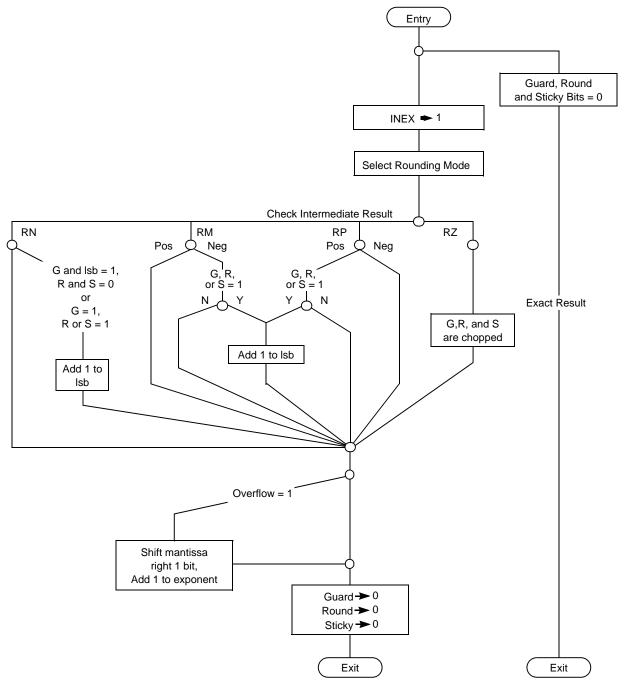

| 65         |                | Rounding the Result                                 |                 |

| 6.5        | _              | g-Point Post-Processing                             |                 |

|            | 6.5.1<br>6.5.2 | Underflow, Round, and Overflow                      |                 |

| 66         |                | Conditional Testing                                 |                 |

| 6.6        | rioating       | g-Point Exceptions                                  |                 |

|            | 6.6.1          | Floating-Point Arithmetic Exceptions                | ر 10 ما<br>د ما |

|            | 6.6.2     | Floating-Point State Frames                                        | 6-23        |

|------------|-----------|--------------------------------------------------------------------|-------------|

| 6.7        | Instructi | ons                                                                | 6-25        |

|            | 6.7.1     | Floating-Point Instruction Overview                                | 6-25        |

|            | 6.7.2     | Floating-Point Instruction Execution Timing                        |             |

|            | 6.7.3     | Key Differences between ColdFire and M68000 FPU Programming Models |             |

|            |           | Chapter 7                                                          |             |

| <b>7</b> 1 |           | Local Memory                                                       | <b>7.</b> 1 |

| 7.1        |           | ons between Local Memory Modules                                   |             |

| 7.2        |           | Overview                                                           |             |

| 7.3        |           | Operation                                                          |             |

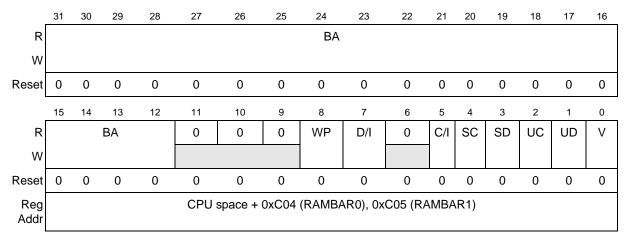

| 7.4        |           | Register Definition                                                |             |

| 7.5        | 7.4.1     | SRAM Base Address Registers (RAMBAR0/RAMBAR1)                      |             |

| 7.5        |           | nitialization                                                      |             |

| 7.0        | 7.5.1     | SRAM Initialization Code                                           |             |

| 7.6        |           | Inagement                                                          |             |

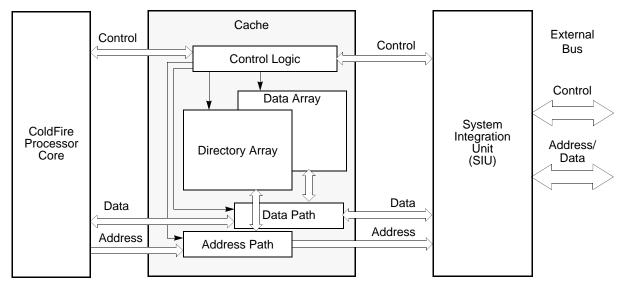

| 7.7        |           | verview                                                            |             |

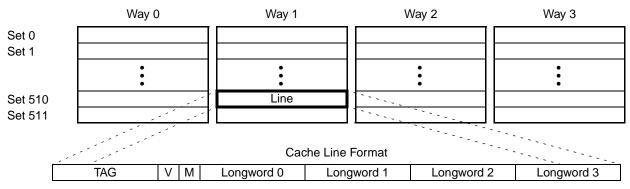

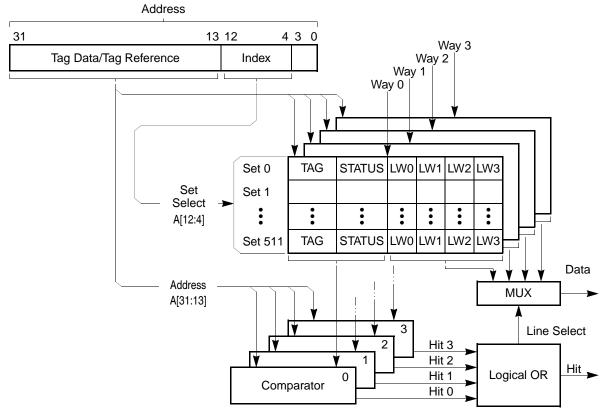

| 7.8        |           | rganization                                                        |             |

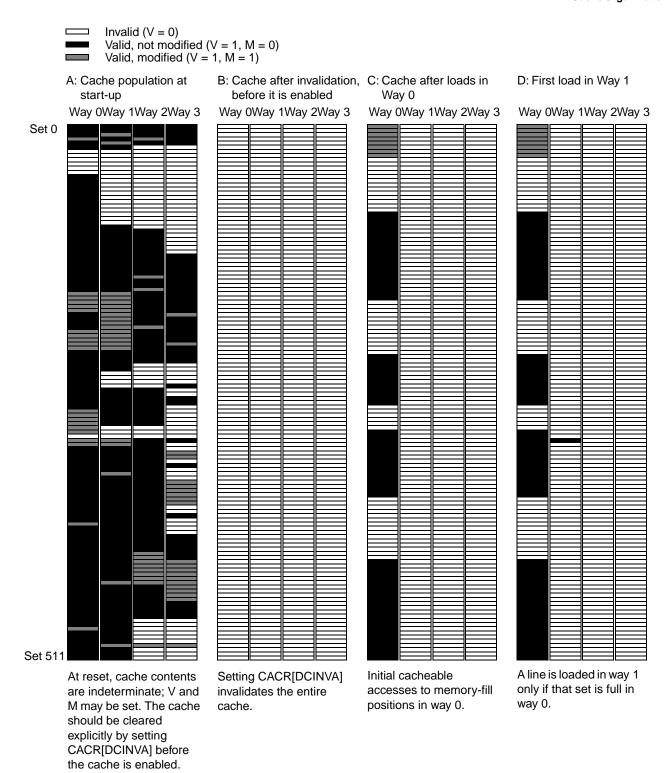

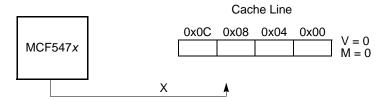

|            | 7.8.1     | Cache Line States: Invalid, Valid-Unmodified, and Valid-Modified   |             |

| 7.0        | 7.8.2     | The Cache at Start-Up                                              |             |

| 7.9        |           | peration                                                           |             |

|            | 7.9.1     | Caching Modes                                                      |             |

|            | 7.9.2     | Cache Protocol                                                     |             |

|            | 7.9.3     | Cache Coherency (Data Cache Only)                                  |             |

|            | 7.9.4     | Memory Accesses for Cache Maintenance                              |             |

| 7.10       | 7.9.5     | Cache Locking                                                      |             |

| 7.10       |           | egister Definition                                                 |             |

|            | 7.10.1    | $\mathcal{U}$                                                      |             |

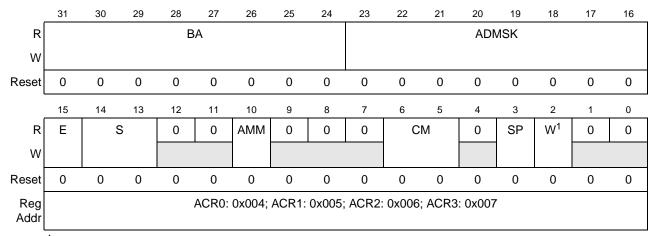

| 7 11       | 7.10.2    | Access Control Registers (ACR0–ACR3)                               |             |

| 7.11       |           | Innagement                                                         |             |

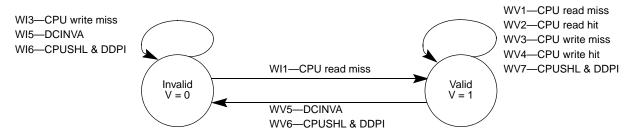

| 7.12       |           | peration Summary                                                   |             |

|            |           |                                                                    |             |

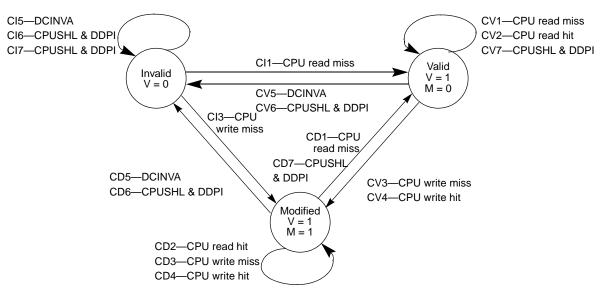

| 7 12       | 7.12.2    | Data Cache State Transitions                                       |             |

| 7.13       | Cache II  | nitialization Code                                                 | /-30        |

|            |           | Chapter 8                                                          |             |

| 0.1        | T . 1     | Debug Support                                                      | 0.1         |

| 8.1        |           | tion                                                               |             |

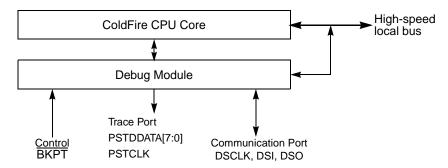

| 0.0        | 8.1.1     | Overview                                                           |             |

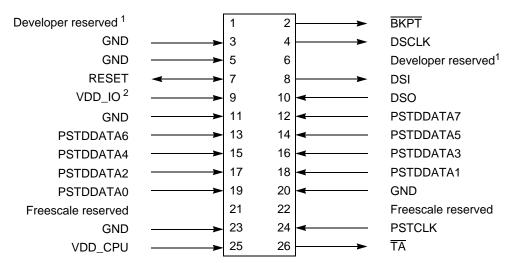

| 8.2        |           | Descriptions                                                       |             |

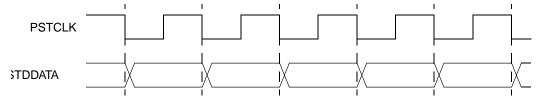

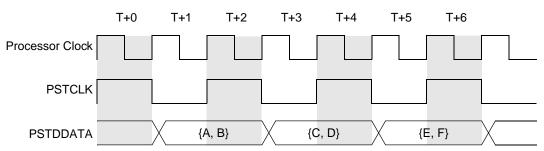

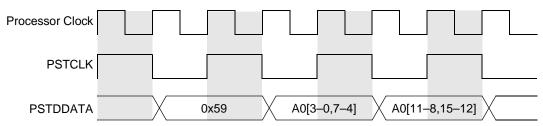

| 0.2        | 8.2.1     | Processor Status/Debug Data (PSTDDATA[7:0])                        |             |

| 8.3        |           | ne Trace Support                                                   | 8-5         |

|            | 8.3.1     | Begin Execution of Taken Branch (PST = 0x5)                        |             |

|            | 8.3.2     | Processor Stopped or Breakpoint State Change (PST = 0xE)           |             |

|            | 8.3.3     | Processor Halted (PST = $0xF$ )                                    | 8-8         |

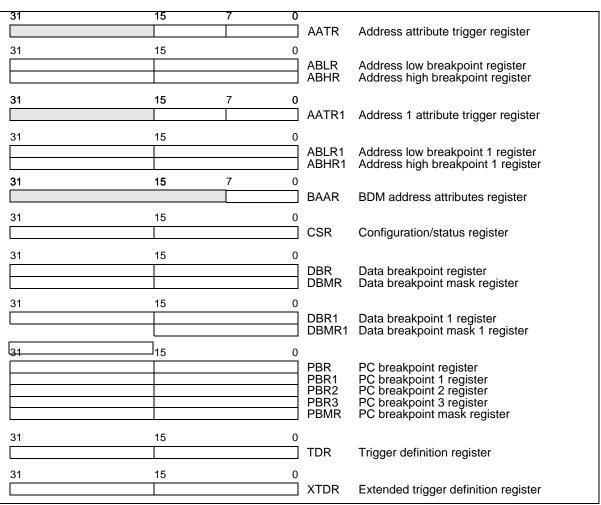

| 8.4  | Memory    | Map/Register Definition                                    | 8-9  |

|------|-----------|------------------------------------------------------------|------|

|      | 8.4.1     | Revision A Shared Debug Resources                          | 8-11 |

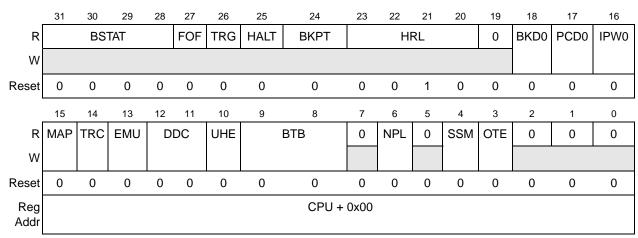

|      | 8.4.2     | Configuration/Status Register (CSR)                        | 8-11 |

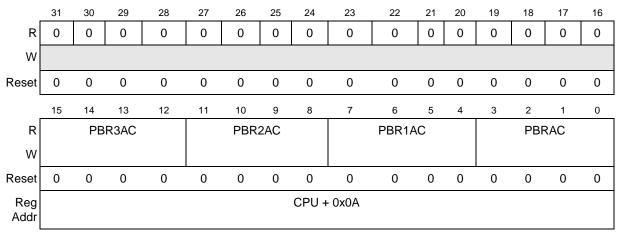

|      | 8.4.3     | PC Breakpoint ASID Control Register (PBAC)                 | 8-14 |

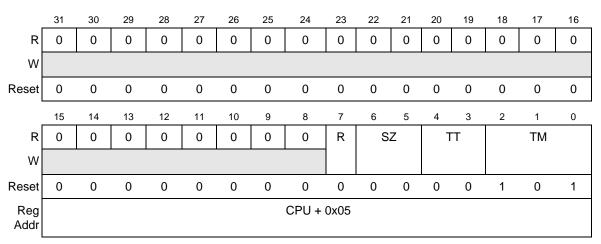

|      | 8.4.4     | BDM Address Attribute Register (BAAR)                      | 8-15 |

|      | 8.4.5     | Address Attribute Trigger Registers (AATR, AATR1)          | 8-16 |

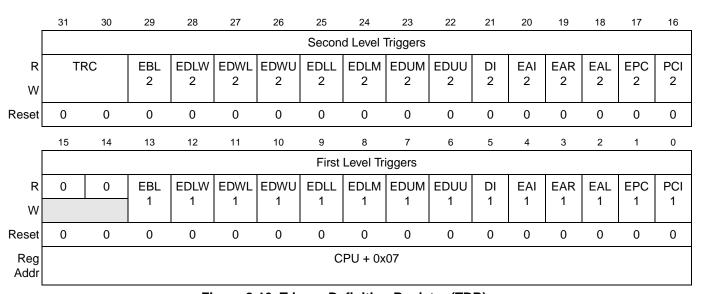

|      | 8.4.6     | Trigger Definition Register (TDR)                          |      |

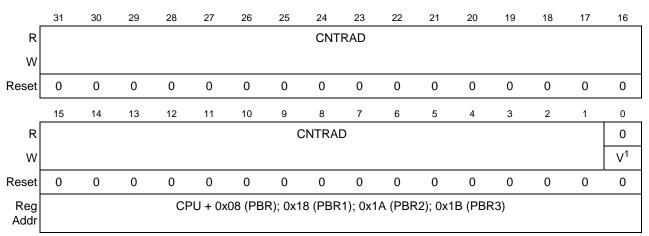

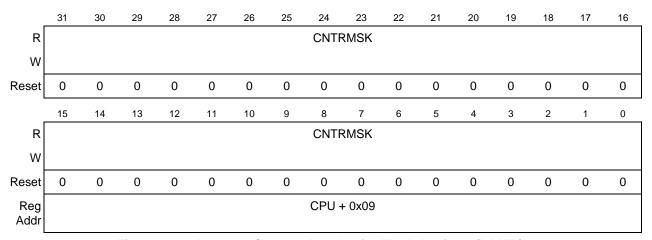

|      | 8.4.7     | Program Counter Breakpoint and Mask Registers (PBRn, PBMR) | 8-20 |

|      | 8.4.8     | Address Breakpoint Registers (ABLR/ABLR1, ABHR/ABHR1)      | 8-21 |

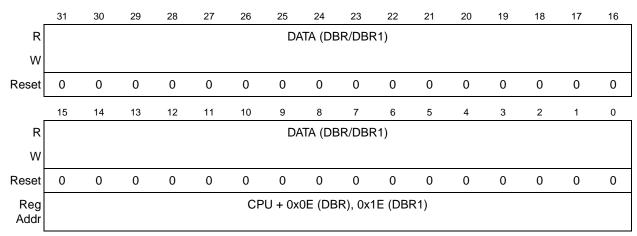

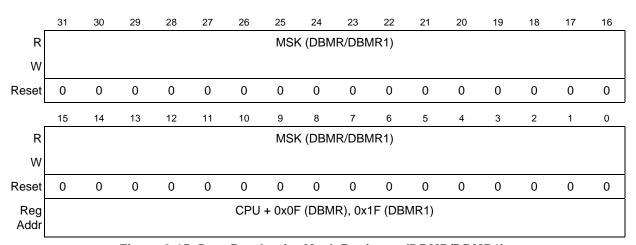

|      | 8.4.9     | Data Breakpoint and Mask Registers (DBR/DBR1, DBMR/DBMR1)  | 8-22 |

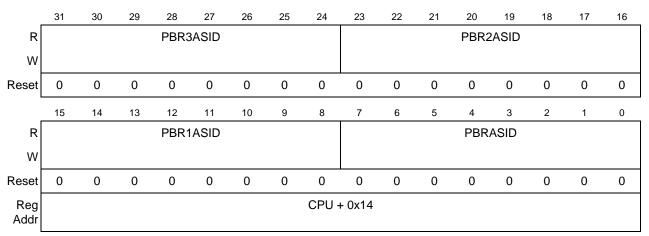

|      | 8.4.10    | PC Breakpoint ASID Register (PBASID)                       | 8-24 |

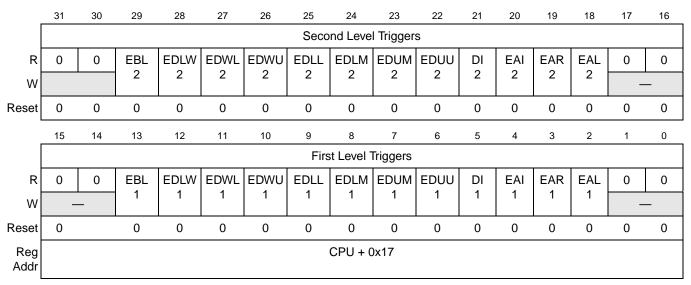

|      | 8.4.11    | Extended Trigger Definition Register (XTDR)                | 8-25 |

| 8.5  | Backgrou  | und Debug Mode (BDM)                                       | 8-28 |

|      | 8.5.1     | CPU Halt                                                   | 8-28 |

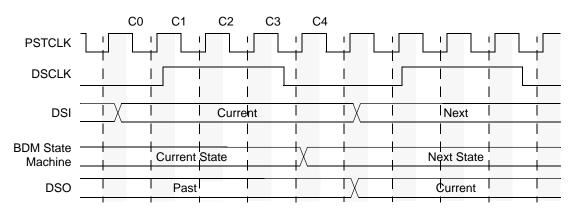

|      | 8.5.2     | BDM Serial Interface                                       | 8-30 |

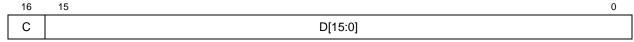

|      | 8.5.3     | BDM Command Set                                            | 8-31 |

| 8.6  | Real-Tin  | ne Debug Support                                           | 8-51 |

|      | 8.6.1     | Theory of Operation                                        | 8-51 |

|      | 8.6.2     | Concurrent BDM and Processor Operation                     | 8-54 |

| 8.7  | Debug C   | Definition of PSTDDATA Outputs                             | 8-54 |

|      | 8.7.1     | User Instruction Set                                       |      |

|      | 8.7.2     | Supervisor Instruction Set                                 | 8-60 |

| 8.8  |           | Debug History                                              |      |

|      | 8.8.1     | ColdFire Debug Classic: The Original Definition            |      |

|      | 8.8.2     | ColdFire Debug Revision B                                  |      |

|      | 8.8.3     | ColdFire Debug Revision C                                  |      |

| 8.9  | Freescale | e-Recommended BDM Pinout                                   | 8-63 |

|      |           | Chapter 9                                                  |      |

|      |           | System Integration Unit (SIU)                              |      |

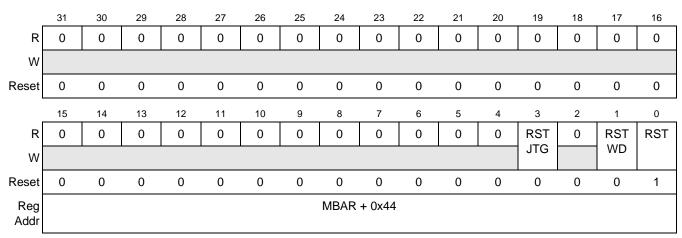

| 9.1  | Introduct | tion                                                       | 9-1  |

| 9.2  |           |                                                            |      |

| 9.3  | Memory    | Map/Register Definition                                    | 9-1  |

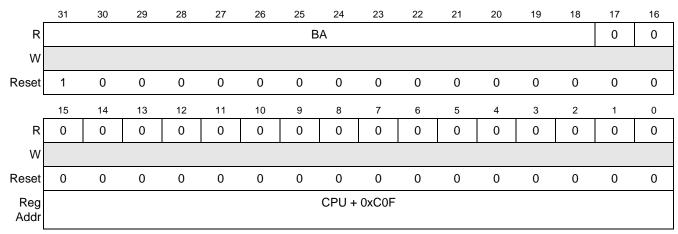

|      | 9.3.1     | Module Base Address Register (MBAR)                        | 9-2  |

|      |           | Chapter 10                                                 |      |

|      |           | Internal Clocks and Bus Architecture                       |      |

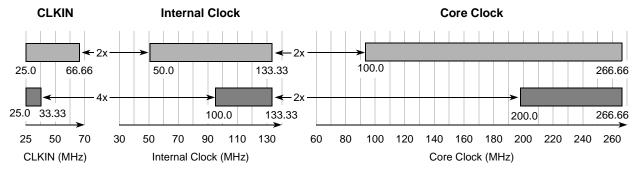

| 10.1 |           | tion                                                       |      |

|      | 10.1.1    | Block Diagram                                              |      |

|      | 10.1.2    | Clocking Overview                                          |      |

|      | 10.1.3    | Internal Bus Overview                                      |      |

|      | 10.1.4    | XL Bus Features                                            |      |

|      | 10.1.5    | Internal Bus Transaction Summaries                         |      |

| 40 - | 10.1.6    | XL Bus Interface Operations                                |      |

| 10.2 | PLL       |                                                            | 10-5 |

|      | 10.2.1 PLL Memory Map/Register Descriptions         | 10-5 |

|------|-----------------------------------------------------|------|

|      | 10.2.2 System PLL Control Register (SPCR)           |      |

| 10.3 | XL Bus Arbiter                                      |      |

|      | 10.3.1 Features                                     | 10-6 |

|      | 10.3.2 Arbiter Functional Description               | 10-6 |

|      | 10.3.3 XLB Arbiter Register Descriptions            | 10-8 |

|      | Chanter 44                                          |      |

|      | Chapter 11 General Purpose Timers (GPT)             |      |

| 11.1 | Introduction                                        | 11-1 |

|      | 11.1.1 Overview                                     | 11-1 |

|      | 11.1.2 Modes of Operation                           | 11-1 |

| 11.2 |                                                     |      |

| 11.3 | Memory Map/Register Definition                      | 11-2 |

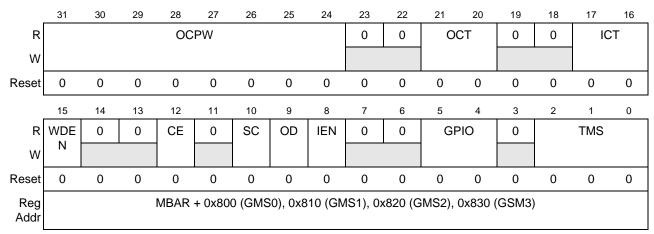

|      | 11.3.1 GPT Enable and Mode Select Register (GMSn)   | 11-3 |

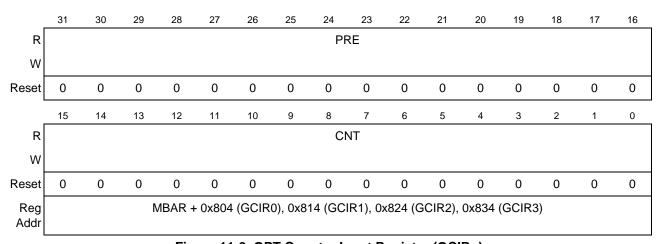

|      | 11.3.2 GPT Counter Input Register (GCIRn)           | 11-5 |

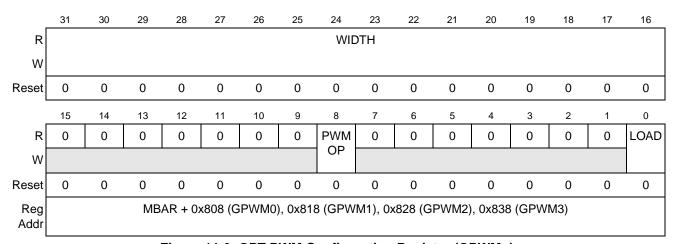

|      | 11.3.3 GPT PWM Configuration Register (GPWMn)       | 11-6 |

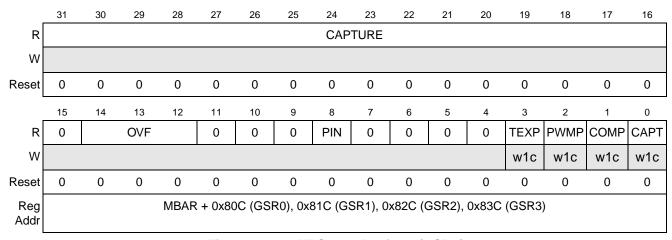

|      | 11.3.4 GPT Status Register (GSRn)                   | 11-7 |

| 11.4 | Functional Description                              |      |

|      | 11.4.1 Timer Configuration Method                   | 11-8 |

|      | 11.4.2 Programming Notes                            | 11-8 |

|      | Chapter 12                                          |      |

|      | Slice Timers (SLT)                                  |      |

| 12.1 |                                                     |      |

|      | 12.1.1 Overview                                     |      |

| 12.2 | Memory Map/Register Definition                      |      |

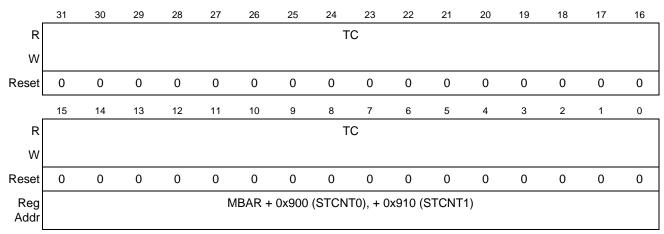

|      | 12.2.1 SLT Terminal Count Register (STCNTn)         |      |

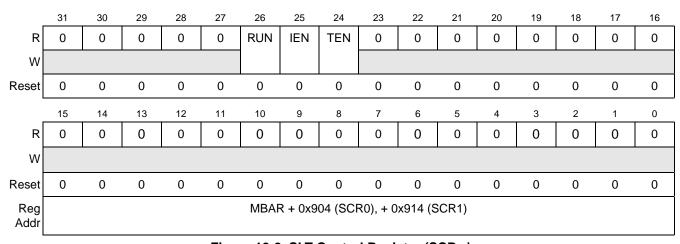

|      | 12.2.2 SLT Control Register (SCRn)                  |      |

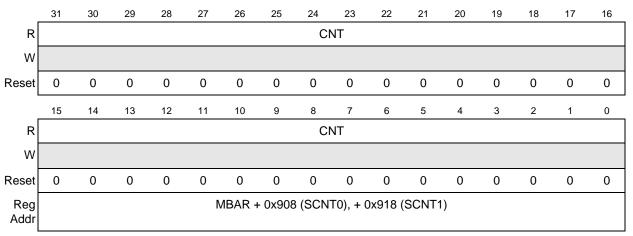

|      | 12.2.3 SLT Timer Count Register (SCNTn)             |      |

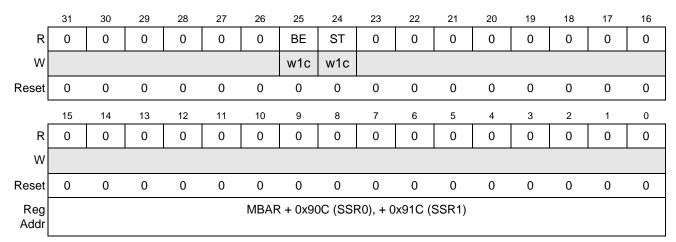

|      | 12.2.4 SLT Status Register (SSRn)                   | 12-4 |

|      | Chapter 13                                          |      |

|      | Interrupt Controller                                |      |

| 13.1 | Introduction                                        |      |

|      | 13.1.1 68K/ColdFire Interrupt Architecture Overview |      |

| 13.2 | Memory Map/Register Descriptions                    |      |

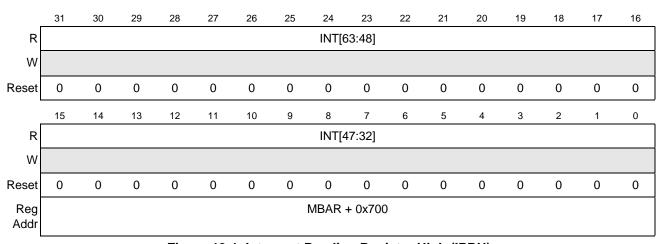

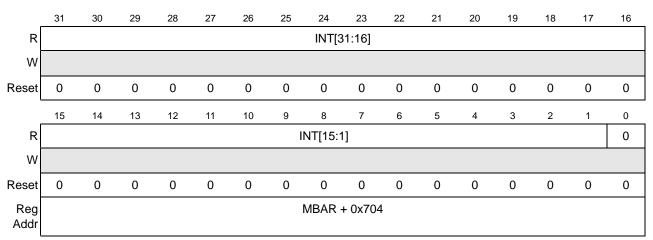

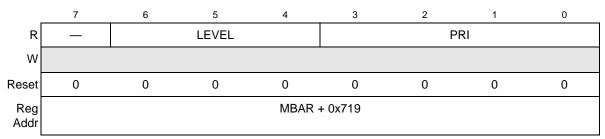

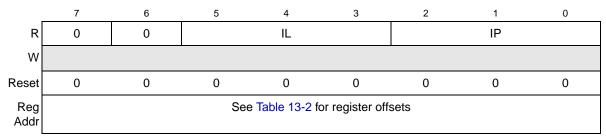

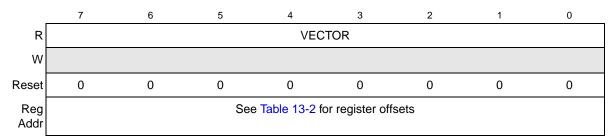

|      | 13.2.1 Register Descriptions                        | 13-6 |

|      | Chapter 14                                          |      |

|      | Edge Port Module (EPORT)                            |      |

|      | Introduction                                        |      |

|      | Interrupt/General-Purpose I/O Pin Descriptions      |      |

| 14.3 | Memory Map/Register Definition                      |      |

|      | 14.3.1 Memory Map                                   | 14-2 |

|      |                                                     |      |

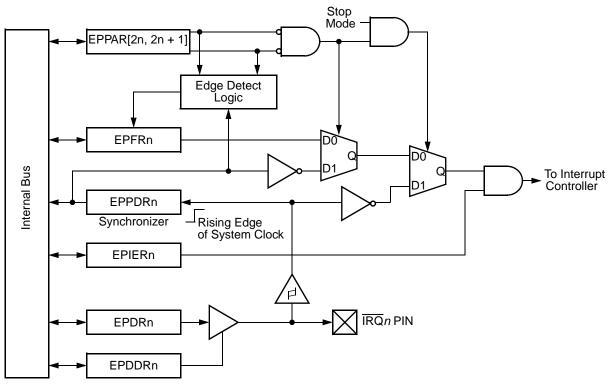

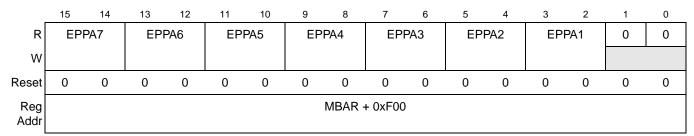

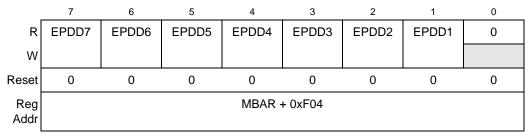

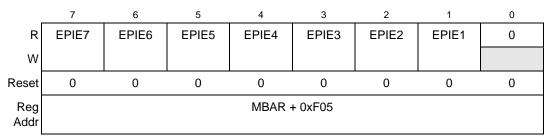

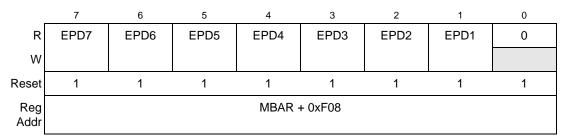

|      | 14.3.2    | Register Descriptions                                            | 14-2  |

|------|-----------|------------------------------------------------------------------|-------|

|      |           | Chapter 15                                                       |       |

|      |           | <b>GPIO</b>                                                      |       |

| 15.1 | Introduct | ion                                                              |       |

|      | 15.1.1    | Overview                                                         |       |

|      | 15.1.2    | Features                                                         |       |

|      |           | Pin Description                                                  |       |

| 15.3 |           | Map/Register Definition                                          |       |

|      | 15.3.1    | Register Overview                                                |       |

|      | 15.3.2    | Register Descriptions                                            |       |

| 15.4 |           | al Description                                                   |       |

|      | 15.4.1    | Overview                                                         | 15-31 |

|      |           | Chapter 16                                                       |       |

|      |           | 32-Kbyte System SRAM                                             |       |

| 16.1 | Introduct | ion                                                              | 16-1  |

|      | 16.1.1    | Block Diagram                                                    |       |

|      | 16.1.2    | Features                                                         |       |

|      | 16.1.3    | Overview                                                         |       |

| 16.2 | Memory    | Map/Register Definition                                          |       |

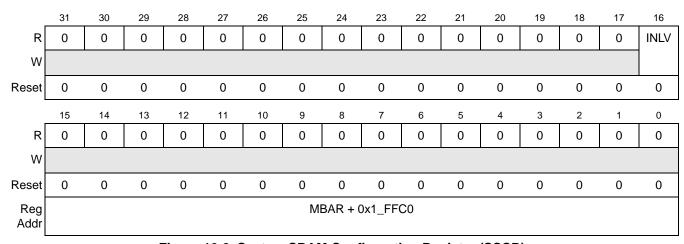

|      | 16.2.1    | System SRAM Configuration Register (SSCR)                        |       |

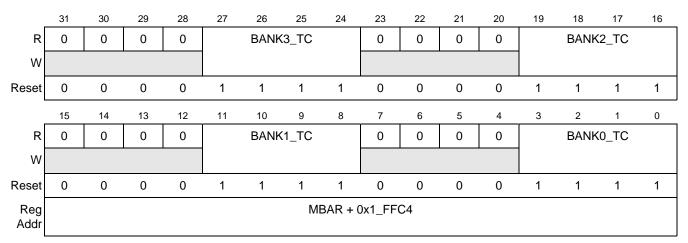

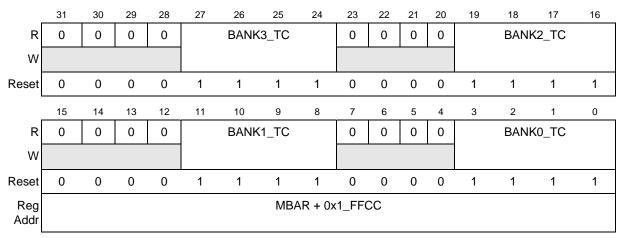

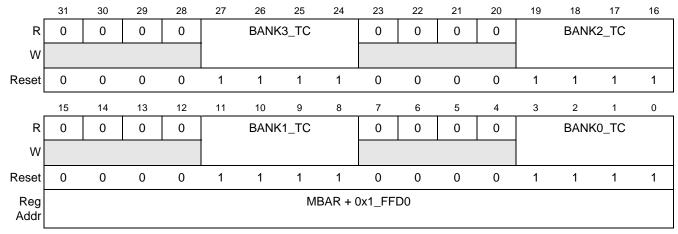

|      | 16.2.2    | Transfer Count Configuration Register (TCCR)                     |       |

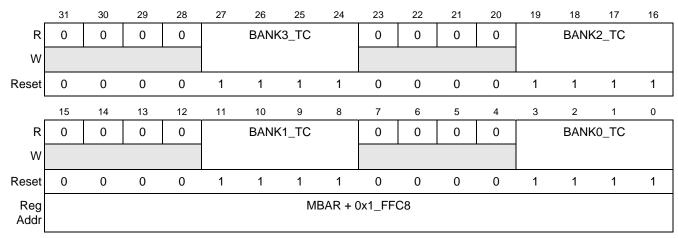

|      | 16.2.3    | Transfer Count Configuration Register—DMA Read Channel (TCCRDR)  |       |

|      | 16.2.4    | Transfer Count Configuration Register—DMA Write Channel (TCCRDW) |       |

|      | 16.2.5    | Transfer Count Configuration Register—SEC (TCCRSEC)              | 16-7  |

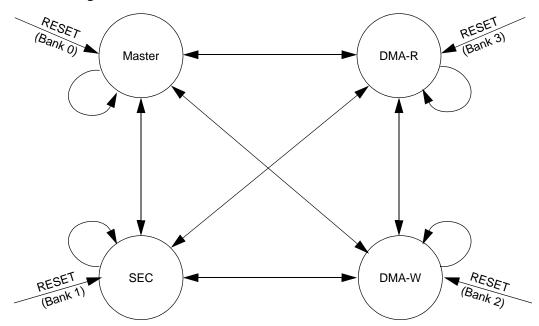

| 16.3 | Function  | al Description                                                   | 16-8  |

|      |           | Chapter 17                                                       |       |

|      |           | FlexBus                                                          |       |

| 17.1 | Introduct | ion                                                              | 17-1  |

|      | 17.1.1    | Overview                                                         | 17-1  |

|      | 17.1.2    | Features                                                         | 17-1  |

|      | 17.1.3    | Modes of Operation                                               | 17-1  |

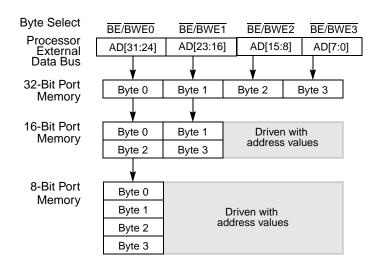

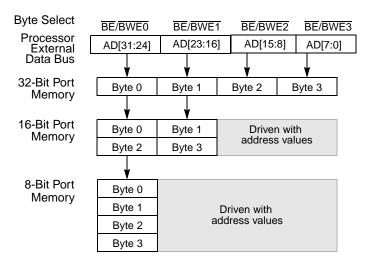

| 17.2 | Byte Lan  | es                                                               | 17-2  |

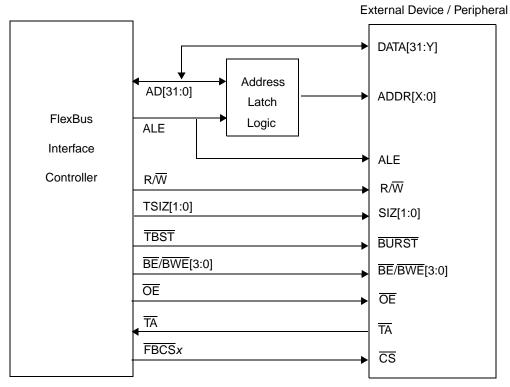

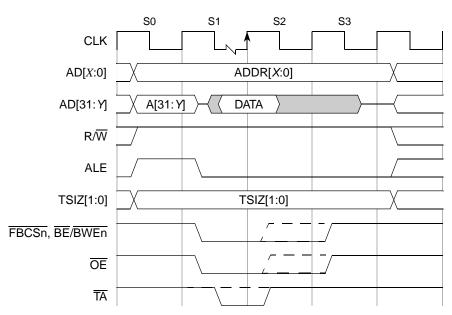

| 17.3 | Address   | Latch                                                            | 17-2  |

| 17.4 | External  | Signals                                                          | 17-3  |

|      | 17.4.1    | Chip-Select (FBCS[5:0])                                          | 17-4  |

|      | 17.4.2    | Address/Data Bus (AD[31:0])                                      | 17-4  |

|      | 17.4.3    | Address Latch Enable (ALE)                                       |       |

|      | 17.4.4    | Read/Write $(\overline{R/W})$                                    |       |

|      | 17.4.5    | Transfer Burst (TBST)                                            | 17-4  |

|      | 17.4.6    | Transfer Size (TSIZ[1:0])                                        | 17-4  |

|      | 17.4.7    | Byte Selects (BE/BWE[3:0])                                       | 17-5  |

|      | 17.4.8    | Output Enable (OE)                                               | 17-5  |

|      |           |                                                                  |       |

|      | 17.4.9    | Transfer Acknowledge (TA)                    | 17-5  |

|------|-----------|----------------------------------------------|-------|

| 17.5 |           | ect Operation                                |       |

|      | 17.5.1    | General Chip-Select Operation                | 17-6  |

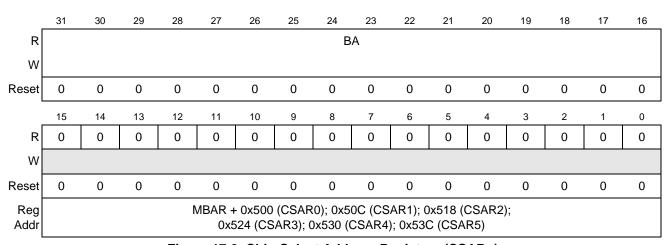

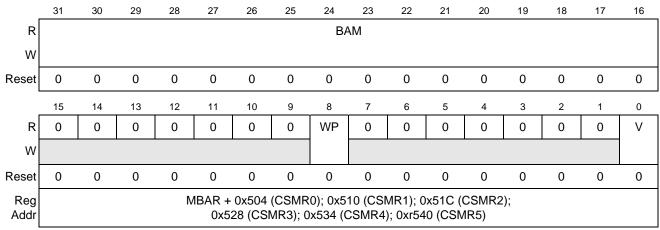

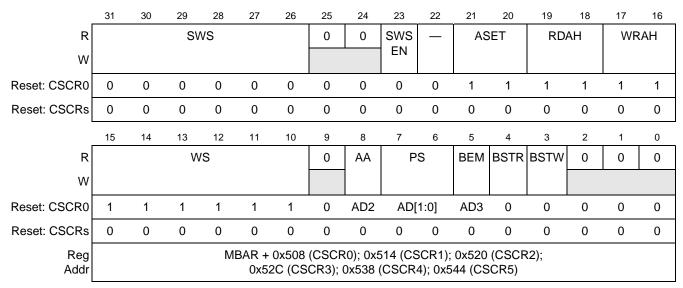

|      | 17.5.2    | Chip-Select Registers                        |       |

| 17.6 | Functiona | al Description                               | 17-12 |

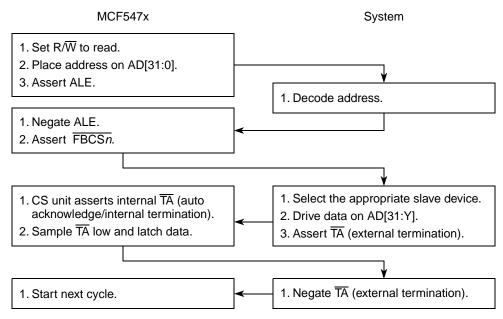

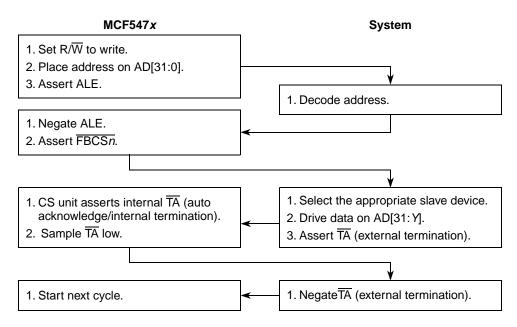

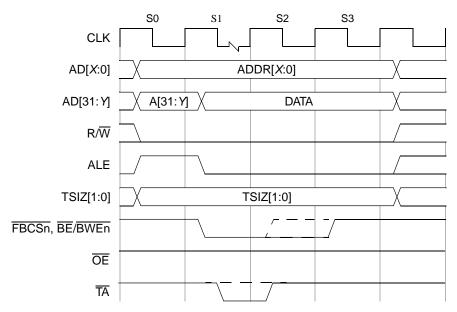

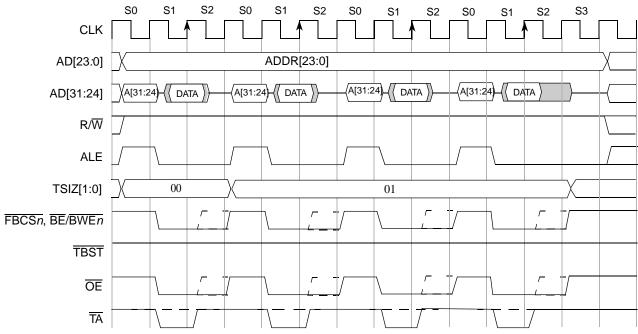

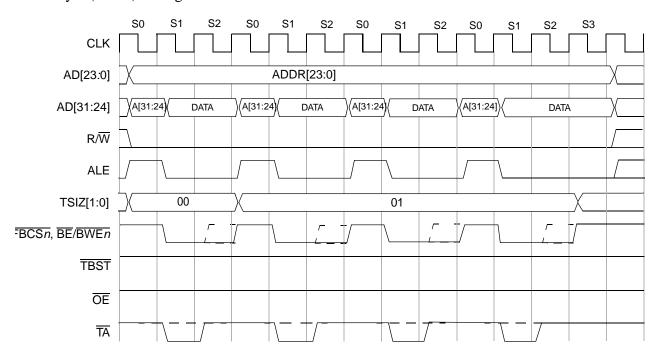

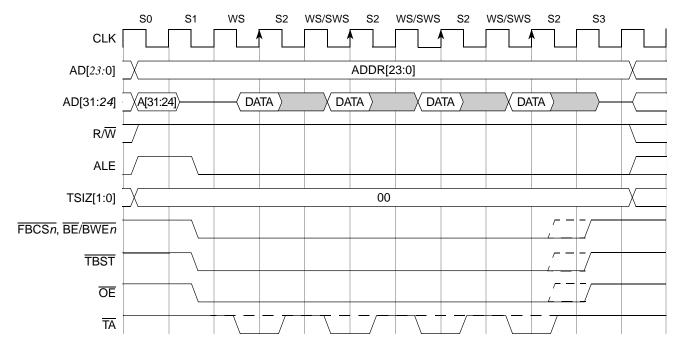

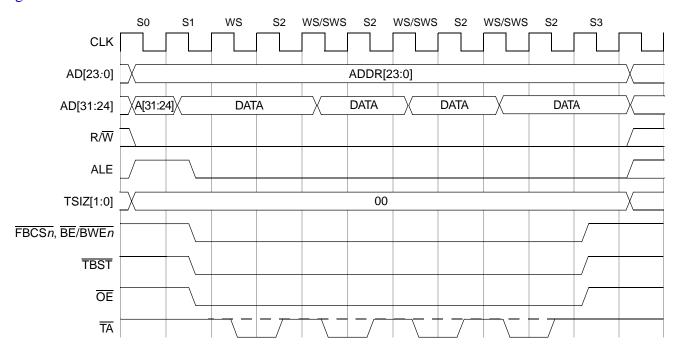

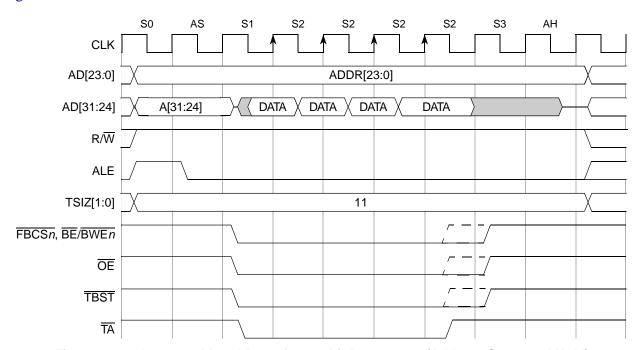

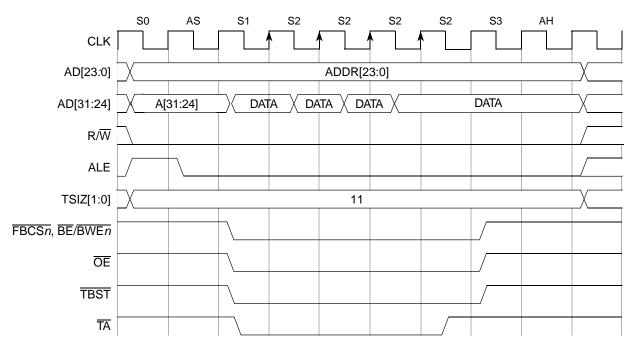

|      | 17.6.1    | Data Transfer Operation                      | 17-12 |

|      | 17.6.2    | Data Byte Alignment and Physical Connections | 17-12 |

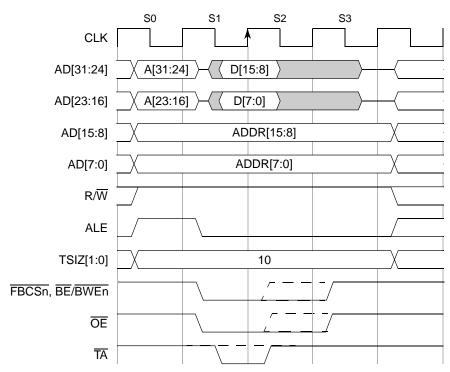

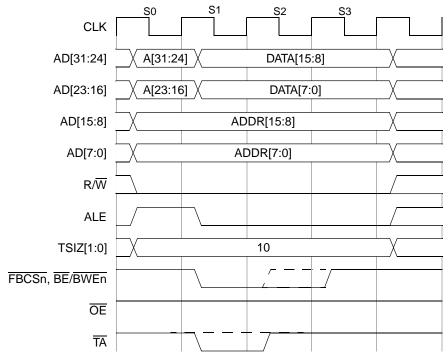

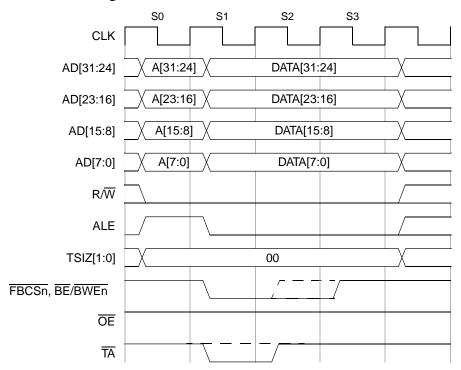

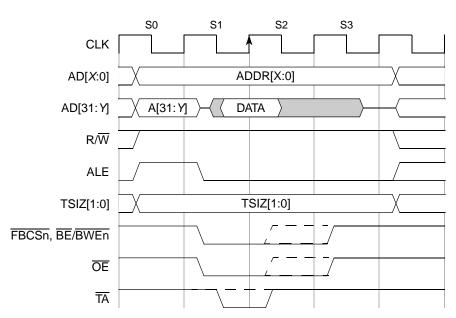

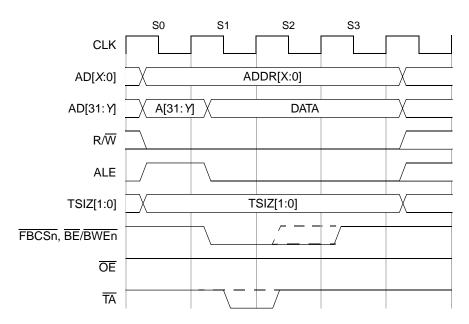

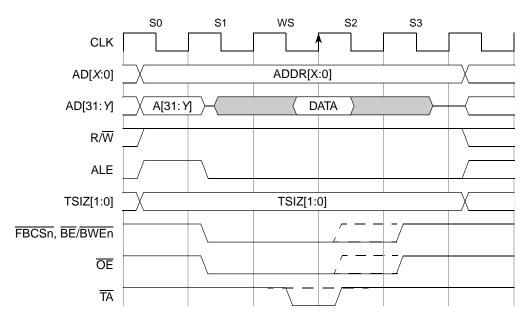

|      | 17.6.3    | Address/Data Bus Multiplexing                | 17-13 |

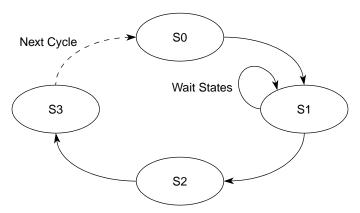

|      | 17.6.4    | Bus Cycle Execution                          |       |

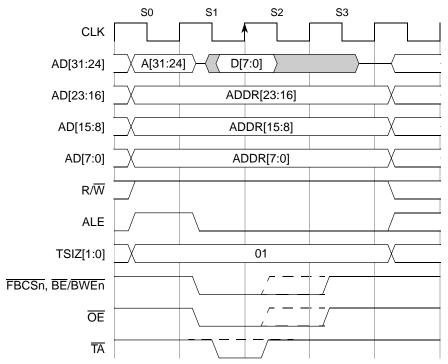

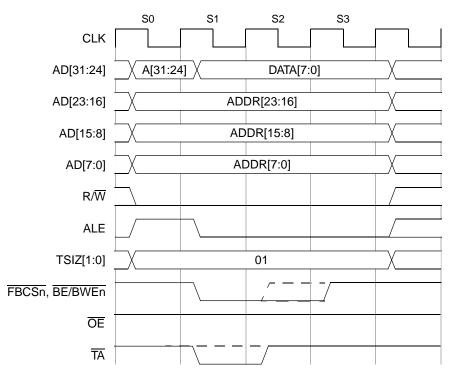

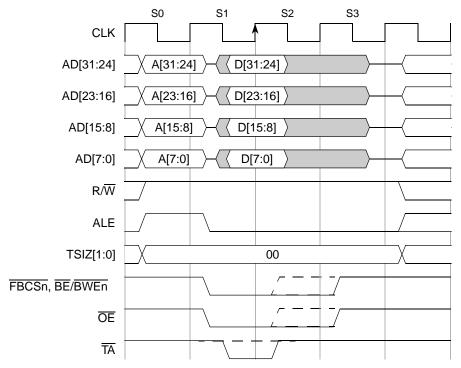

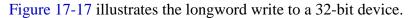

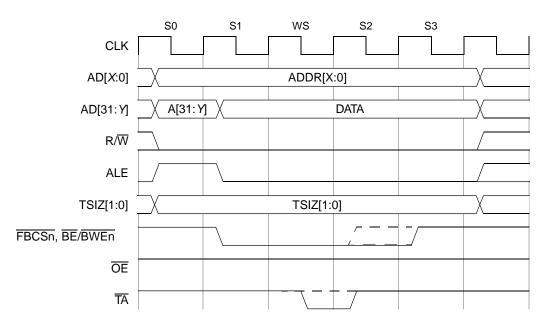

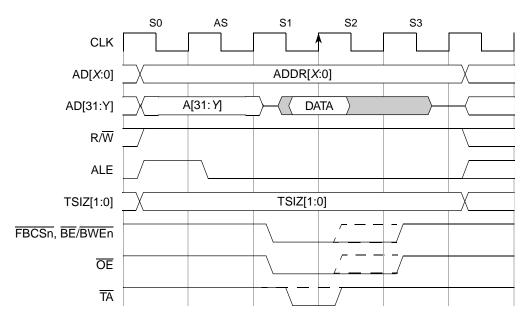

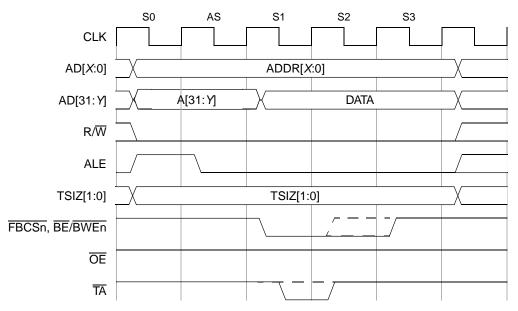

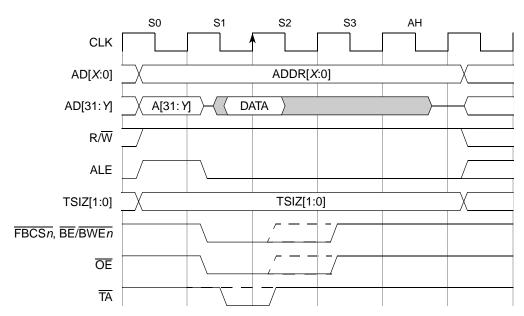

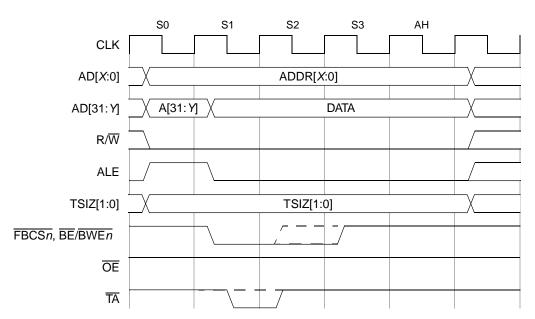

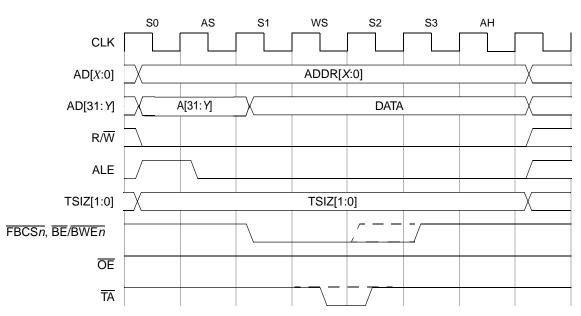

|      | 17.6.5    | FlexBus Timing Examples                      |       |

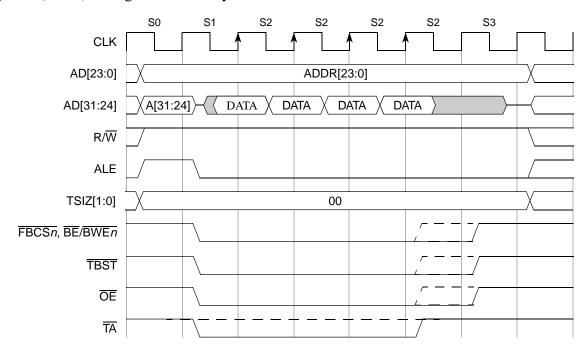

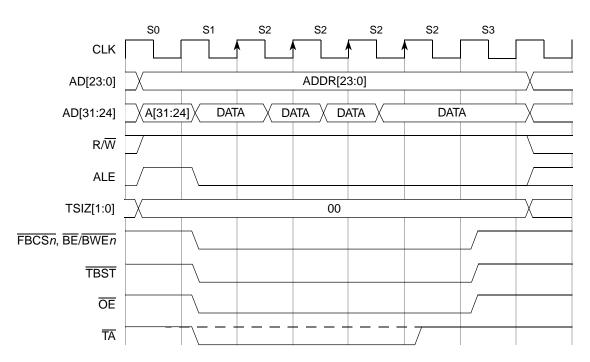

|      | 17.6.6    | Burst Cycles                                 | 17-26 |

|      | 17.6.7    | Misaligned Operands                          | 17-31 |

|      | 17.6.8    | Bus Errors                                   | 17-32 |

|      |           | Objected 40                                  |       |

|      |           | Chapter 18                                   |       |

| 18 1 | Introduct | SDRAM Controller (SDRAMC)                    | 18-1  |

|      |           | <i>I</i>                                     |       |

| 10.2 | 18.2.1    | Features                                     |       |

|      | 18.2.2    | Terminology                                  |       |

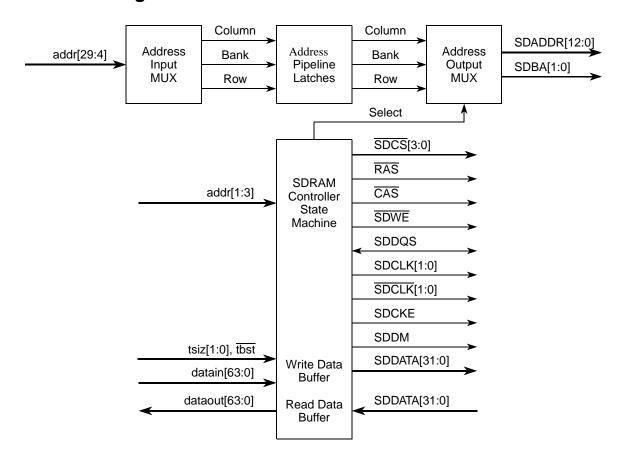

|      | 18.2.3    | Block Diagram                                |       |

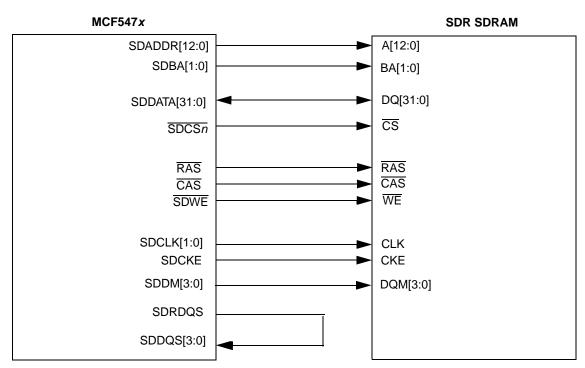

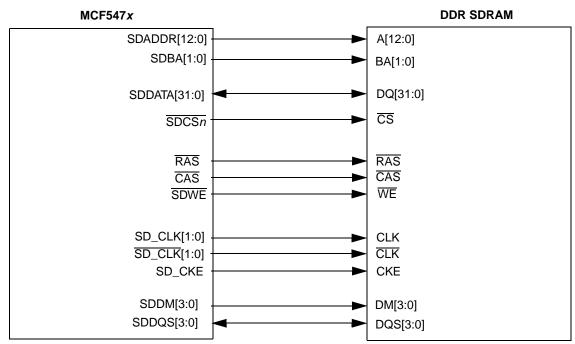

| 18.3 |           | Signal Description                           |       |

|      | 18.3.1    | SDRAM Data Bus (SDDATA[31:0])                |       |

|      | 18.3.2    | SDRAM Address Bus (SDADDR[12:0])             |       |

|      | 18.3.3    | SDRAM Bank Addresses (SDBA[1:0])             |       |

|      | 18.3.4    | SDRAM Row Address Strobe (RAS)               | 18-3  |

|      | 18.3.5    | SDRAM Column Address Strobe (CAS)            | 18-3  |

|      | 18.3.6    | SDRAM Chip Selects (SDCS[3:0])               | 18-3  |

|      | 18.3.7    | SDRAM Write Data Byte Mask (SDDM[3:0])       | 18-3  |

|      | 18.3.8    | SDRAM Data Strobe (SDDQS[3:0])               | 18-3  |

|      | 18.3.9    | SDRAM Clock (SDCLK[1:0])                     |       |

|      |           | Inverted SDRAM Clock (SDCLK[1:0])            |       |

|      |           | SDRAM Write Enable (SDWE)                    |       |

|      |           | SDRAM Clock Enable (SDCKE)                   |       |

|      |           | SDR SDRAM Data Strobe (SDRDQS)               |       |

|      |           | SDRAM Memory Supply (SDVDD)                  |       |

|      |           | SDRAM Reference Voltage (VREF)               |       |

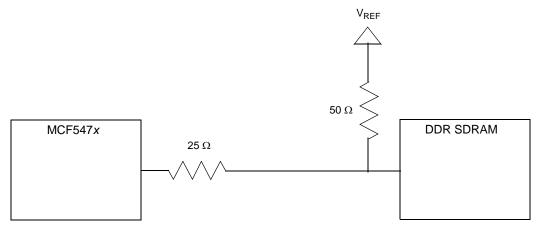

| 18.4 |           | Recommendations                              |       |

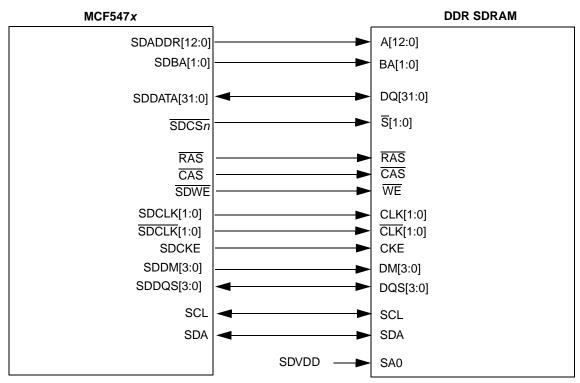

|      | 18.4.1    | Supported Memory Configurations              |       |

|      | 18.4.2    | SDRAM SDR Connections                        |       |

|      | 18.4.3    | SDRAM DDR Component Connections              |       |

|      | 18.4.4    | SDRAM DDR DIMM Connections                   |       |

| 10.5 | 18.4.5    | DDR SDRAM Layout Considerations              |       |

| 18.5 |           | Overview                                     |       |

|      | 18.5.1    | SDRAM Commands                               | 18-9  |

|      | 18.5.2      | Power-Up Initialization                                           | 18-13 |

|------|-------------|-------------------------------------------------------------------|-------|

| 18.6 | Functiona   | ıl Overview                                                       | 18-15 |

|      | 18.6.1      | Page Management                                                   | 18-15 |

|      | 18.6.2      | Transfer Size                                                     |       |

| 18.7 | Memory 1    | Map/Register Definition                                           | 18-16 |

|      | 18.7.1      | SDRAM Drive Strength Register (SDRAMDS)                           | 18-16 |

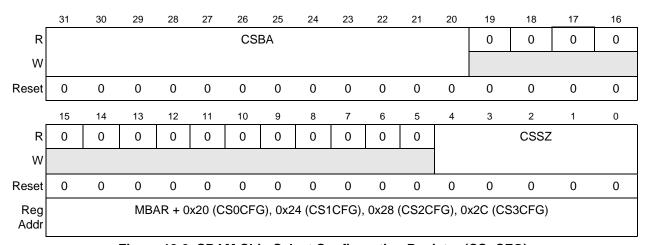

|      | 18.7.2      | SDRAM Chip Select Configuration Registers (CSnCFG)                | 18-17 |

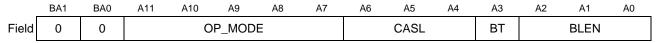

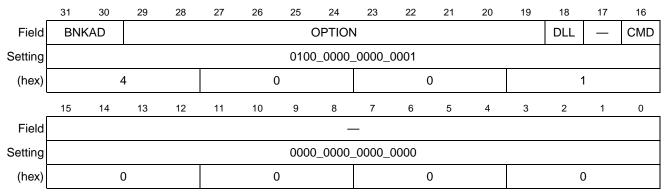

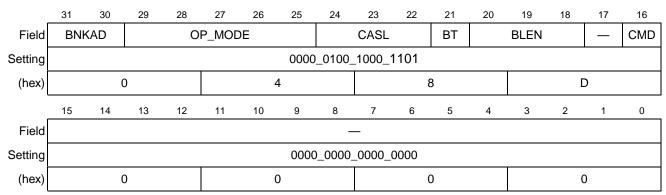

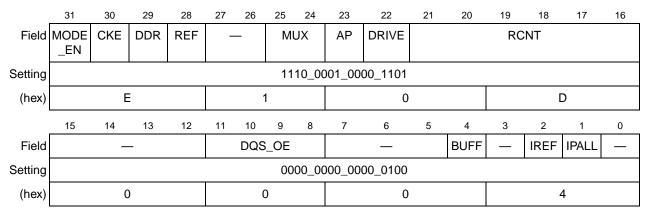

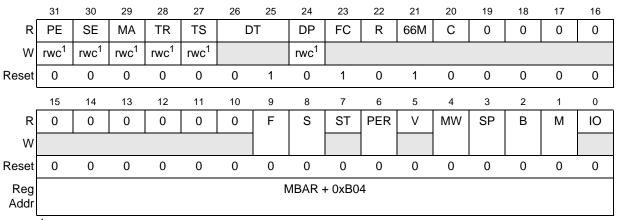

|      | 18.7.3      | SDRAM Mode/Extended Mode Register (SDMR)                          | 18-18 |

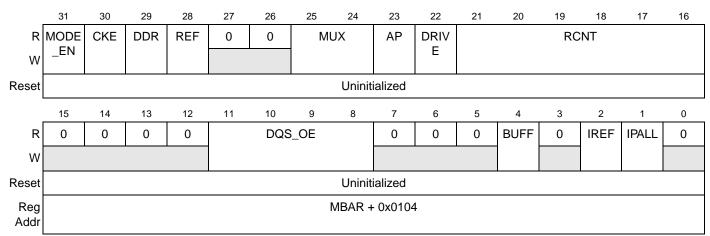

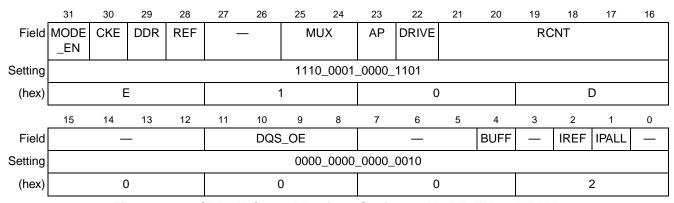

|      | 18.7.4      | SDRAM Control Register (SDCR)                                     | 18-19 |

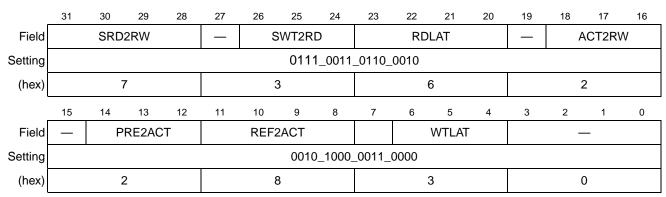

|      | 18.7.5      | SDRAM Configuration Register 1 (SDCFG1)                           |       |

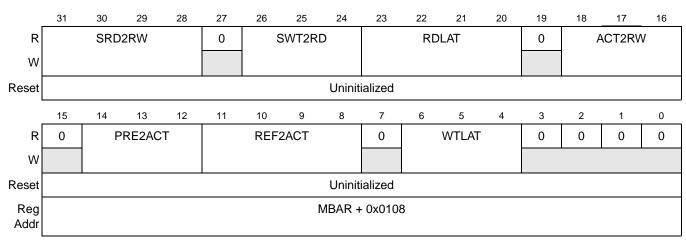

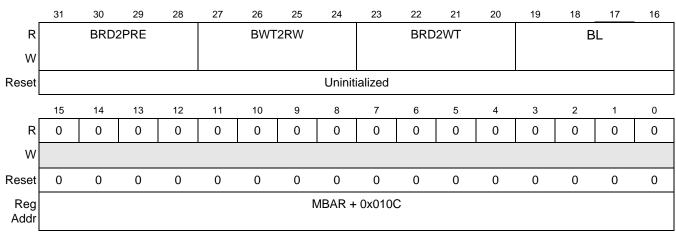

|      | 18.7.6      | SDRAM Configuration Register 2 (SDCFG2)                           | 18-23 |

| 18.8 | SDRAM       | Example                                                           | 18-24 |

|      | 18.8.1      | SDRAM Signal Drive Strength Settings                              |       |

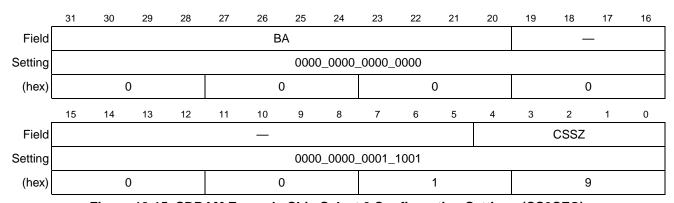

|      | 18.8.2      | SDRAM Chip Select Settings                                        |       |

|      | 18.8.3      | SDRAM Configuration 1 Register Settings                           |       |

|      | 18.8.4      | SDRAM Configuration 2 Register Settings                           |       |

|      | 18.8.5      | SDRAM Control Register Settings and PALL command                  |       |

|      | 18.8.6      | Set the Extended Mode Register                                    |       |

|      | 18.8.7      | Set the Mode Register and Reset DLL                               |       |

|      | 18.8.8      | Issue a PALL command                                              |       |

|      | 18.8.9      | Perform Two Refresh Cycles                                        |       |

|      | 18.8.10     | Clear the Reset DLL Bit in the Mode Register                      |       |

|      | 18.8.11     | Enable Automatic Refresh and Lock Mode Register                   |       |

|      | 18.8.12     | Initialization Code                                               | 18-33 |

|      |             | Chapter 10                                                        |       |

|      |             | Chapter 19                                                        |       |

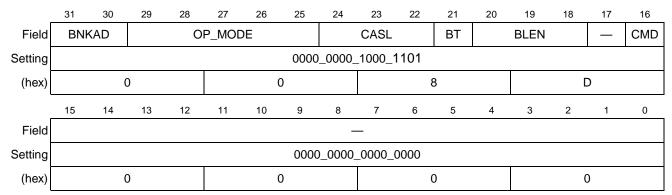

| 10.1 | Introduceti | PCI Bus Controller                                                | 10.1  |

| 19.1 |             | on                                                                |       |

|      | 19.1.1      | $\epsilon$                                                        |       |

|      | 19.1.2      | Overview                                                          |       |

| 10.2 | 19.1.3      | Features                                                          |       |

| 19.2 | 19.2.1      | Signal Description                                                |       |

|      | 19.2.1      | Command/Byte Enables (PCICXBE[3:0])                               |       |

|      | 19.2.2      | Device Select (PCIDEVSEL)                                         |       |

|      | 19.2.3      | Frame (PCIFRAME)                                                  |       |

|      | 19.2.4      | Initialization Device Select (PCIIDSEL)                           |       |

|      | 19.2.5      | Initiatization Device Select (FCHDSEL)  Initiator Ready (PCIIRDY) |       |

|      | 19.2.7      | Parity (PCIPAR)                                                   |       |

|      | 19.2.7      | PCI Clock (CLKIN)                                                 |       |

|      | 19.2.8      | Parity Error (PCIPERR)                                            |       |

|      | 19.2.9      | Reset (PCIRESET)                                                  |       |

|      | 19.2.10     | System Error (PCISERR)                                            |       |

|      | 19.2.11     | Stop (PCISTOP)                                                    |       |

|      | 19.2.12     | Target Ready (PCITRDY)                                            |       |

|      | 17.20.10    |                                                                   | 1     |

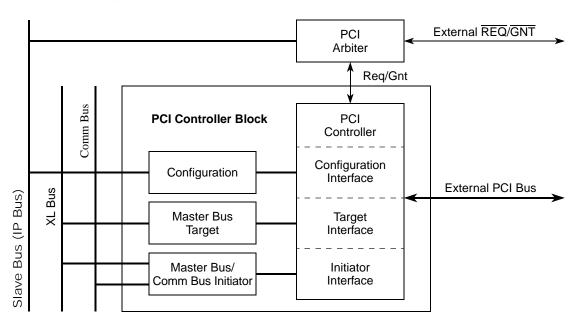

| 19.3 | Memory           | Map/Register Definition                              | 19-4  |

|------|------------------|------------------------------------------------------|-------|

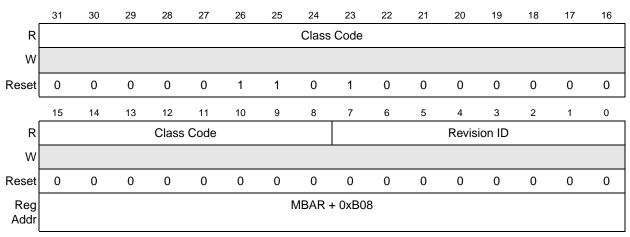

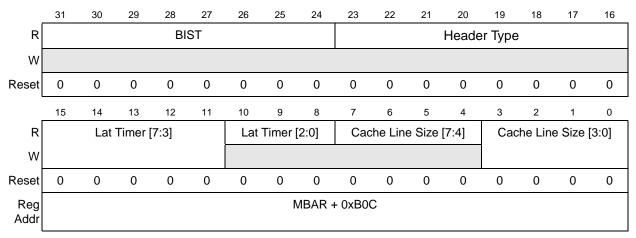

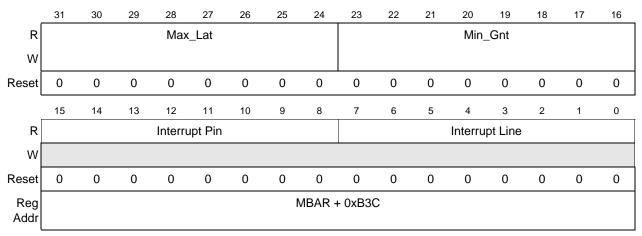

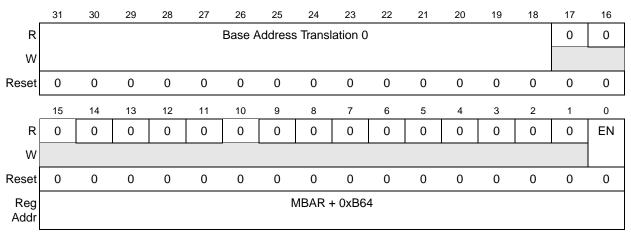

|      | 19.3.1           | PCI Type 0 Configuration Registers                   | 19-6  |

|      | 19.3.2           | General Control/Status Registers                     | 19-13 |

|      | 19.3.3           | Communication Subsystem Interface Registers          | 19-23 |

| 19.4 | Function         | al Description                                       |       |

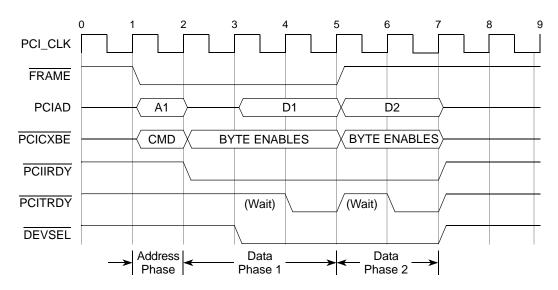

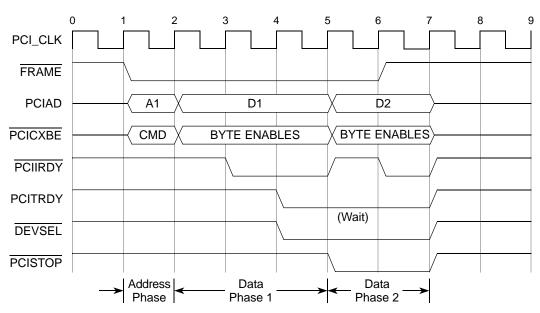

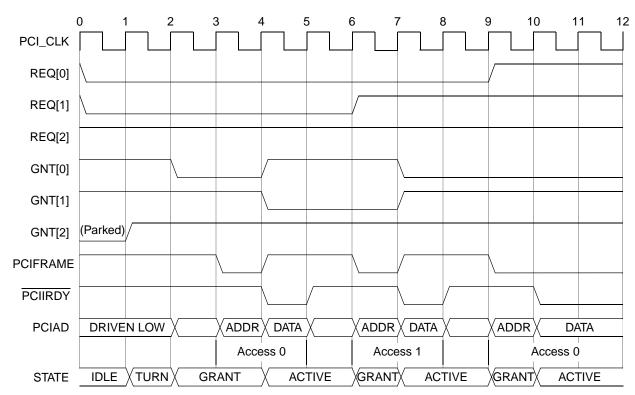

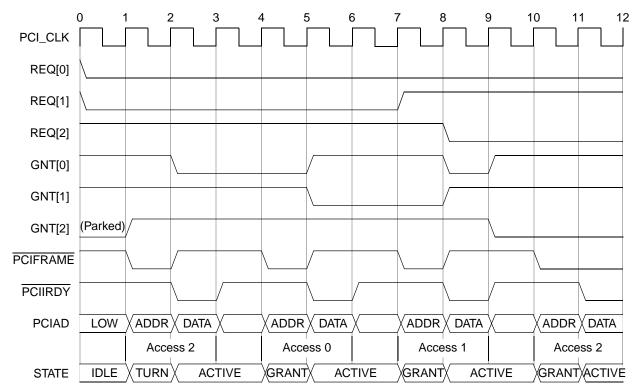

|      | 19.4.1           | PCI Bus Protocol                                     |       |

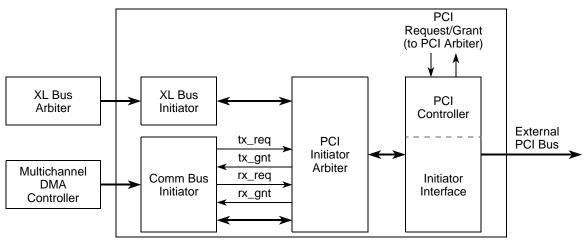

|      | 19.4.2           | Initiator Arbitration                                | 19-55 |

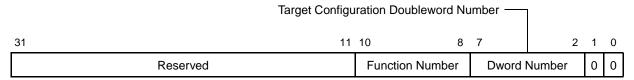

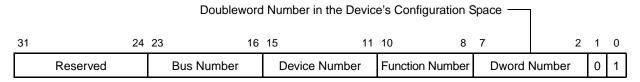

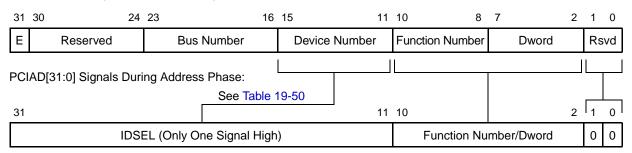

|      | 19.4.3           | Configuration Interface                              | 19-56 |

|      | 19.4.4           | XL Bus Initiator Interface                           | 19-56 |

|      | 19.4.5           | XL Bus Target Interface                              | 19-63 |

|      | 19.4.6           | Communication Subsystem Initiator Interface          | 19-66 |

|      | 19.4.7           | PCI Clock Scheme                                     | 19-70 |

|      | 19.4.8           | Interrupts                                           | 19-70 |

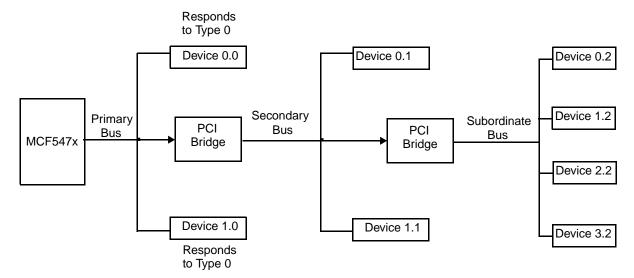

| 19.5 | Applicat         | ion Information                                      | 19-70 |

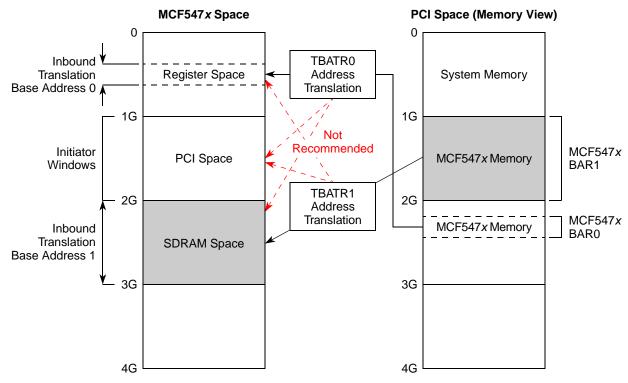

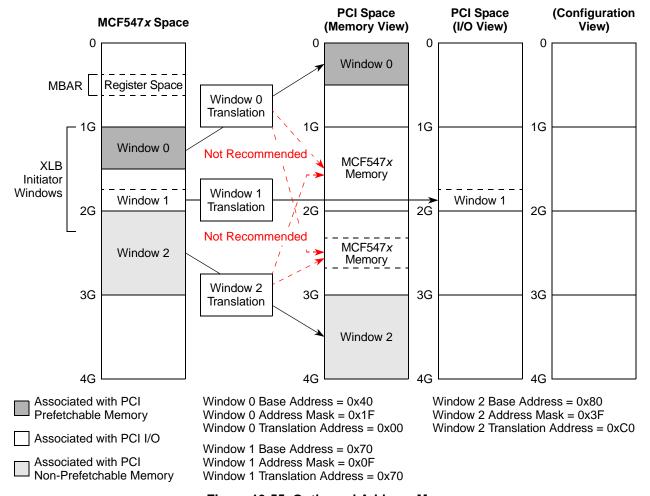

|      | 19.5.1           | XL Bus-Initiated Transaction Mapping                 | 19-70 |

|      | 19.5.2           | Address Maps                                         | 19-71 |

| 19.6 | XL Bus           | Arbitration Priority                                 | 19-75 |

|      |                  | 01 1 00                                              |       |

|      |                  | Chapter 20                                           |       |

| 20.4 |                  | PCI Bus Arbiter Module                               | 20.4  |

| 20.1 |                  | tion                                                 |       |

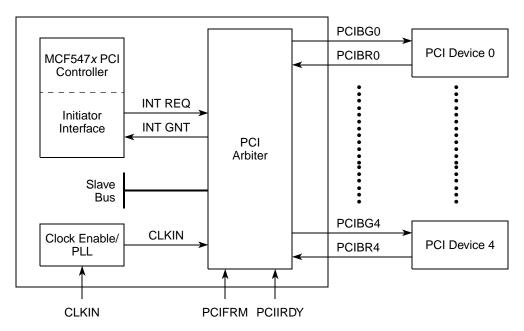

|      | 20.1.1           | Block Diagram                                        |       |

|      | 20.1.2           | Overview                                             |       |

| 20.2 | 20.1.3           | Features                                             |       |

| 20.2 |                  | Signal Description                                   |       |

|      | 20.2.1           | Frame (PCIFRM)                                       |       |

|      | 20.2.2           | Initiator Ready (PCIIRDY)                            |       |

|      | 20.2.3           | PCI Clock (CLKIN)                                    |       |

|      | 20.2.4           | External Bus Grant (PCIBG[4:1])                      |       |

|      | 20.2.5           | External Bus Grant/Request Output (PCIBGO/PCIREQOUT) |       |

|      | 20.2.6<br>20.2.7 | External Bus Request (PCIBR[4:1])                    |       |

| 20.2 |                  | Definition                                           |       |

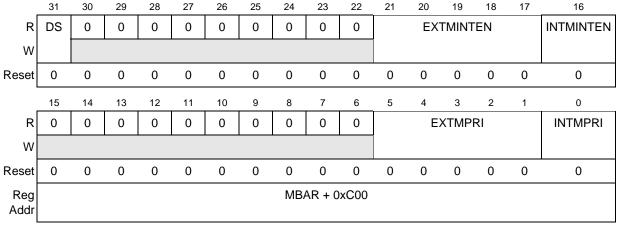

| 20.3 | 20.3.1           | PCI Arbiter Control Register (PACR)                  |       |

|      | 20.3.1           |                                                      |       |

| 20.4 |                  | PCI Arbiter Status Register (PASR)                   |       |

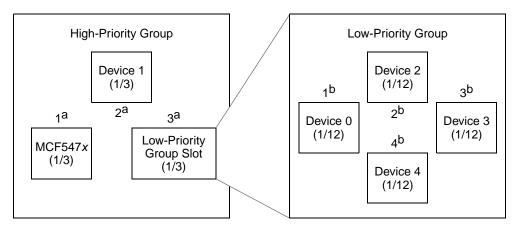

| 20.4 | 20.4.1           | External PCI Requests                                |       |

|      | 20.4.1           | •                                                    |       |

|      | 20.4.2           |                                                      |       |

| 20.5 |                  | Waster Time-Out                                      |       |

|      |                  | S                                                    |       |

| 20.0 | merrupt          | o                                                    | 20-10 |

|      |                  | Chapter 21                                           |       |

|      |                  | Integrated Security Engine (SEC)                     |       |

| 21.1 | Features         |                                                      | 21-1  |

|      |                  |                                                      |       |

| 21.2  | ColdFire    | Security Architecture                        | 21-1    |

|-------|-------------|----------------------------------------------|---------|

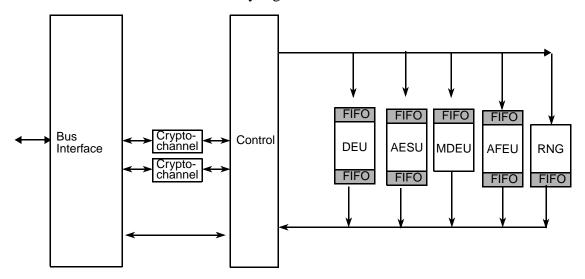

| 21.3  | Block Dia   | agram                                        | 21-2    |

| 21.4  | Overview    | <sup>7</sup>                                 | 21-2    |

|       | 21.4.1      | Bus Interface                                | 21-2    |

|       | 21.4.2      | SEC Controller Unit                          | 21-3    |

|       | 21.4.3      | Crypto-Channels                              | 21-3    |

|       | 21.4.4      | Execution Units (EUs)                        | 21-4    |

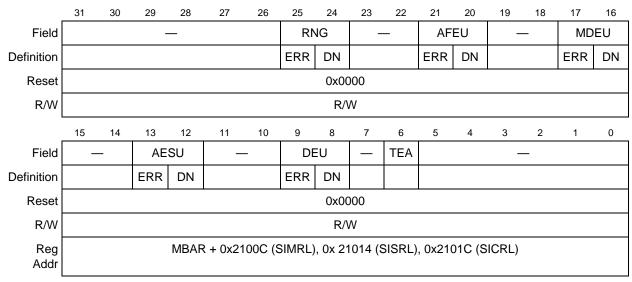

| 21.5  | Memory 1    | Map/Register Definition                      | 21-8    |

| 21.6  | Controlle   | r                                            | . 21-11 |

|       | 21.6.1      | EU Access                                    | . 21-11 |

|       | 21.6.2      | Multiple EU Assignment                       | . 21-11 |

|       | 21.6.3      | Multiple Channels                            | . 21-12 |

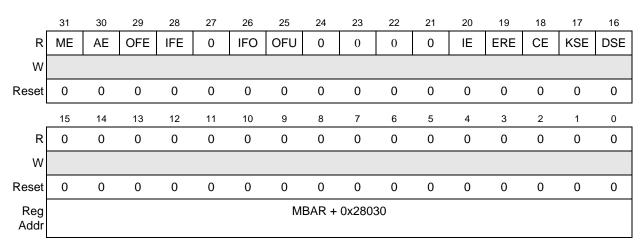

|       | 21.6.4      | Controller Registers                         | . 21-12 |

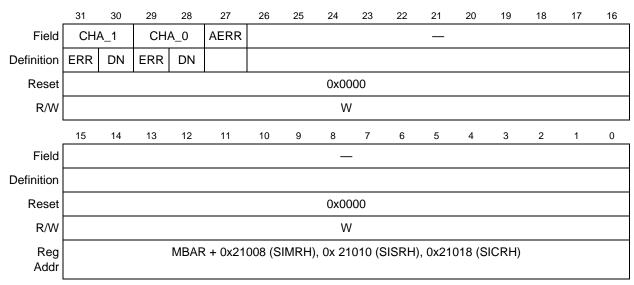

| 21.7  | Channels    |                                              | . 21-18 |

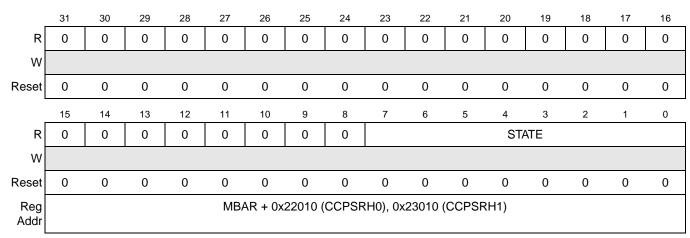

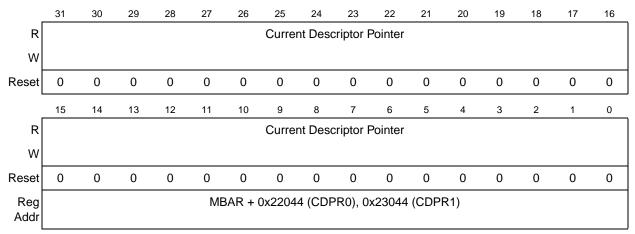

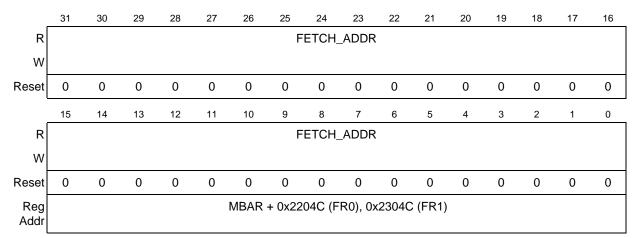

|       | 21.7.1      | Crypto-Channel Registers                     | . 21-19 |

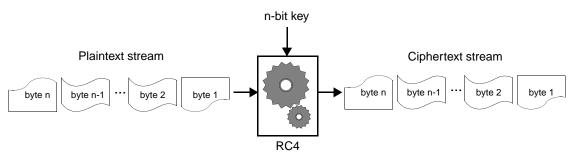

| 21.8  | ARC Fou     | r Execution Unit (AFEU)                      | . 21-28 |

|       | 21.8.1      | AFEU Register Map                            | . 21-28 |

|       | 21.8.2      | AFEU Reset Control Register (AFRCR)          | . 21-28 |

|       | 21.8.3      | AFEU Status Register (AFSR)                  | . 21-29 |

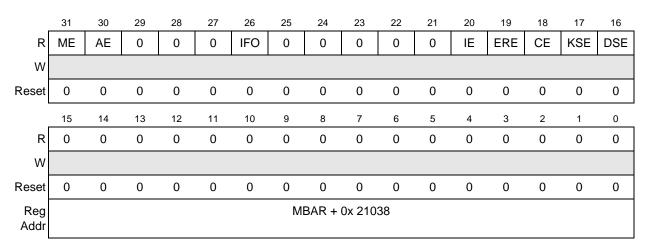

|       | 21.8.4      | AFEU Interrupt Status Register (AFISR)       | . 21-31 |

|       | 21.8.5      | AFEU Interrupt Mask Register (AFIMR)         | . 21-32 |

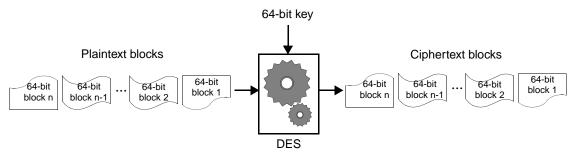

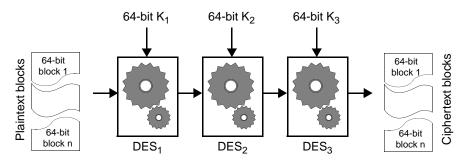

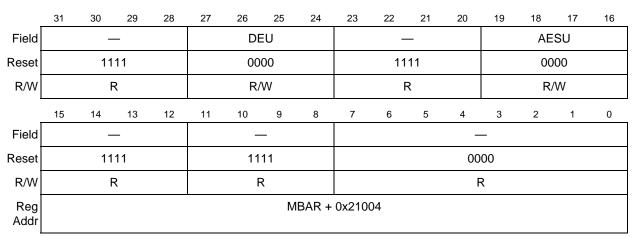

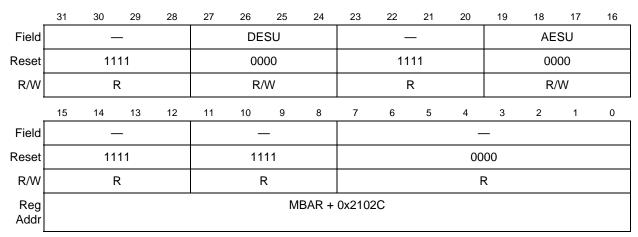

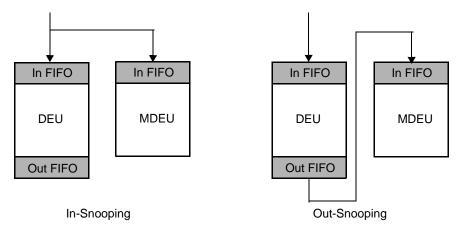

| 21.9  | Data Enci   | ryption Standard Execution Units (DEU)       | . 21-34 |

|       | 21.9.1      | DEU Register Map                             | . 21-34 |

|       | 21.9.2      | DEU Reset Control Register (DRCR)            | . 21-34 |

|       | 21.9.3      | DEU Status Register (DSR)                    | . 21-35 |

|       | 21.9.4      | DEU Interrupt Status Register (DISR)         | . 21-37 |

|       | 21.9.5      | DEU Interrupt Mask Register (DIMR)           | . 21-39 |

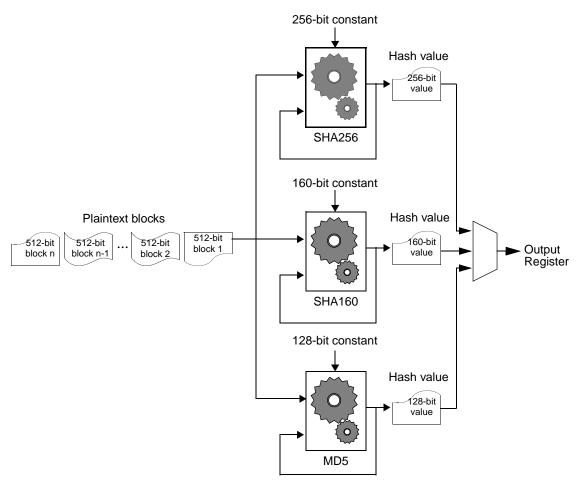

| 21.10 | ) Message 1 | Digest Execution Unit (MDEU)                 | . 21-40 |

|       | 21.10.1     | MDEU Register Map                            | . 21-40 |

|       | 21.10.2     | MDEU Reset Control Register (MDRCR)          | . 21-41 |

|       | 21.10.3     | MDEU Status Register (MDSR)                  | . 21-41 |

|       | 21.10.4     | MDEU Interrupt Status Register (MDISR)       | . 21-43 |

|       | 21.10.5     | MDEU Interrupt Mask Register (MDIMR)         | . 21-44 |

| 21.11 | RNG Exe     | ecution Unit (RNG)                           | . 21-46 |

|       | 21.11.1     | RNG Register Map                             | . 21-46 |

|       | 21.11.2     | RNG Reset Control Register (RNGRCR)          | . 21-46 |

|       | 21.11.3     | RNG Status Register (RNGSR)                  | . 21-47 |

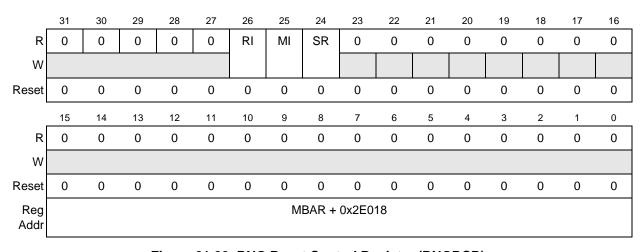

|       | 21.11.4     | RNG Interrupt Status Register (RNGISR)       | . 21-48 |

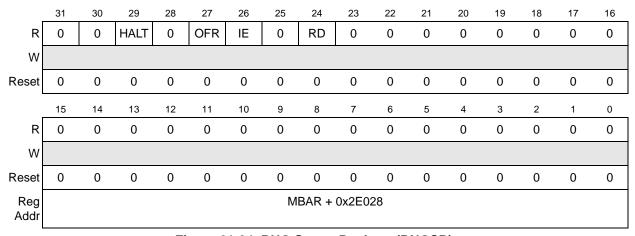

|       | 21.11.5     | RNG Interrupt Mask Register (RNGIMR)         | . 21-49 |

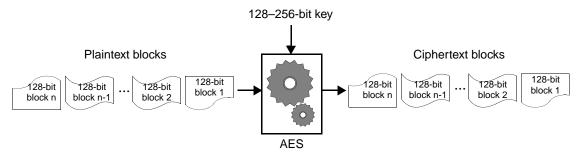

| 21.12 | 2 Advance   | d Encryption Standard Execution Units (AESU) | . 21-50 |

|       | 21.12.1     | AESU Register Map                            | . 21-50 |

|       | 21.12.2     | AESU Reset Control Register (AESRCR)         | . 21-50 |

|       | 21.12.3     | AESU Status Register (AESSR)                 | . 21-51 |

|       |             | AESU Interrupt Status Register (AESISR)      |         |

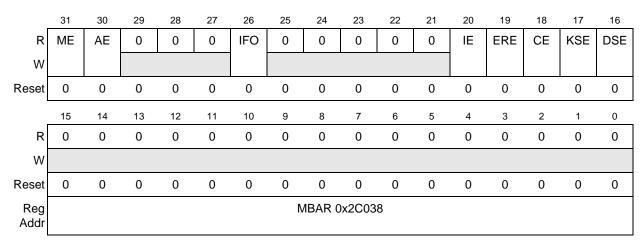

|       | 21.12.5     | AESU Interrupt Mask Register (AESIMR)        | . 21-54 |

|       |             |                                              |         |

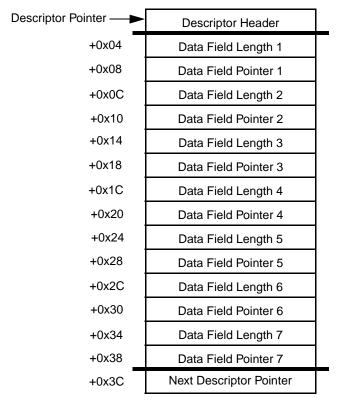

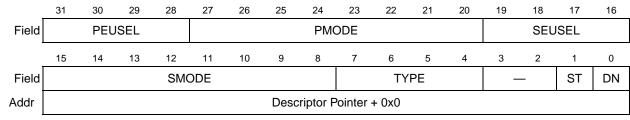

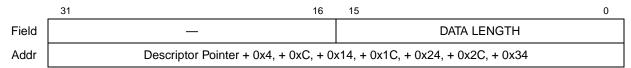

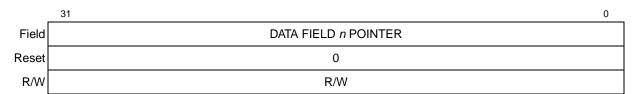

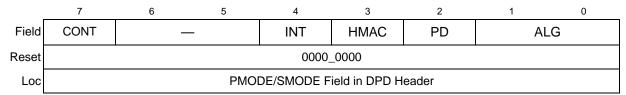

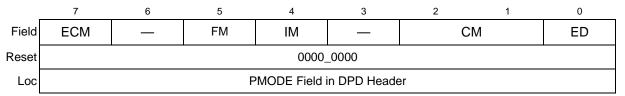

| 21.13 | 3 Descripto | ors                                           | 21-56 |

|-------|-------------|-----------------------------------------------|-------|

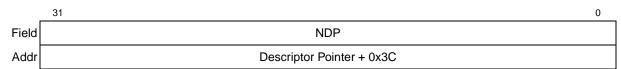

|       | 21.13.1     | Descriptor Structure                          | 21-56 |

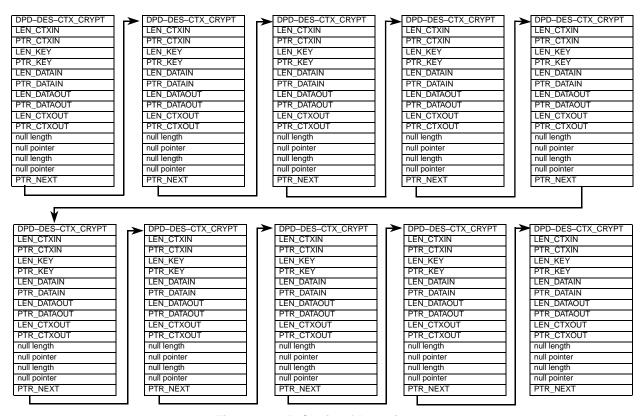

|       | 21.13.2     | Descriptor Chaining                           | 21-61 |

|       |             | Descriptor Type Formats                       |       |

|       |             | Descriptor Classes                            |       |

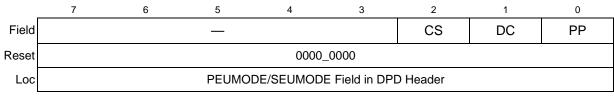

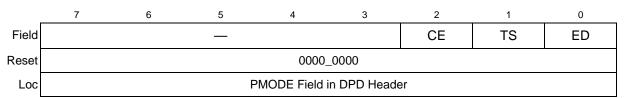

| 21.14 |             | ific Data Packet Descriptors                  |       |

|       |             | AFEU Mode Options and Data Packet Descriptors |       |

|       |             | DEU Mode Options and Data Packet Descriptors  |       |

|       |             | MDEU Mode Options and Data Packet Descriptors |       |

|       |             | RNG Data Packet Descriptors                   |       |

|       |             | AESU Mode Options and Data Packet Descriptors |       |

|       |             | Multi-Function Data Packet Descriptors        |       |

|       | 21.11.0     | Truth T unction But T texet Bescriptors       | 21 )0 |

|       |             | Chapter 22                                    |       |

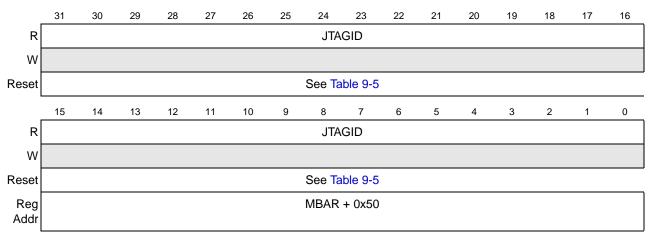

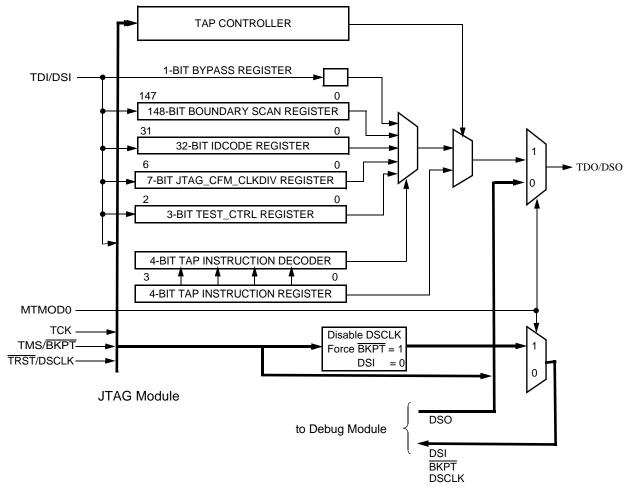

|       |             | IEEE 1149.1 Test Access Port (JTAG)           |       |

| 22.1  | Introducti  | ion                                           | 22-1  |

|       | 22.1.1      | Block Diagram                                 |       |

|       | 22.1.2      | Features                                      |       |

|       | 22.1.3      | Modes of Operation                            |       |

| 22.2  |             | Signal Description                            |       |

|       | 22.2.1      | Detailed Signal Description                   |       |

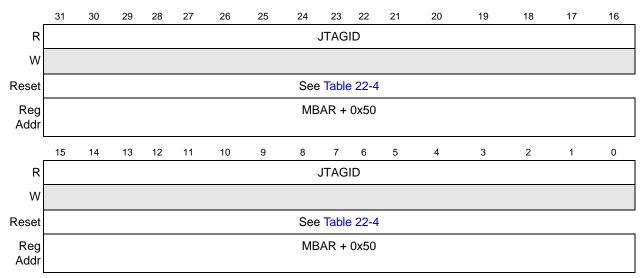

| 22.3  |             | Map/Register Definition                       |       |

|       | 22.3.1      | Memory Map                                    |       |

|       | 22.3.2      | Register Descriptions                         |       |

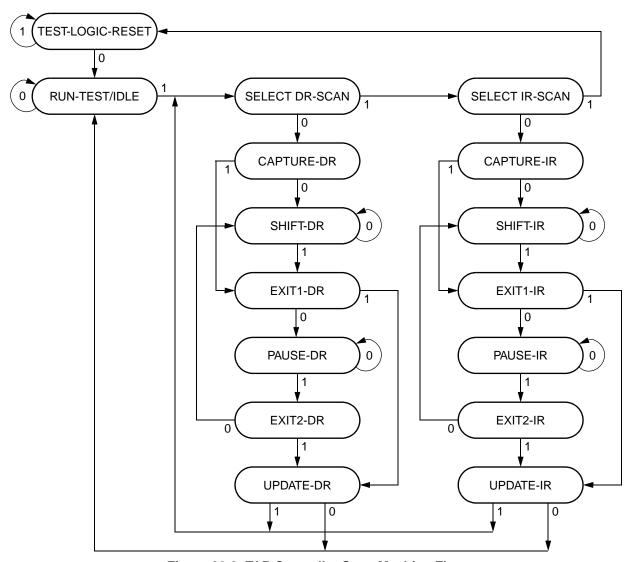

| 22.4  |             | al Description                                |       |

|       | 22.4.1      | JTAG Module                                   |       |

|       | 22.4.2      | TAP Controller                                |       |

|       | 22.4.3      | JTAG Instructions                             |       |

| 22.5  |             | ion/Application Information                   |       |

| 22.5  | 22.5.1      | Restrictions                                  |       |

|       | 22.5.2      | Nonscan Chain Operation                       |       |

|       | 22.3.2      | Tronscan Chain Operation                      |       |

|       |             | Chapter 23                                    |       |

|       |             | Multichannel DMA                              |       |

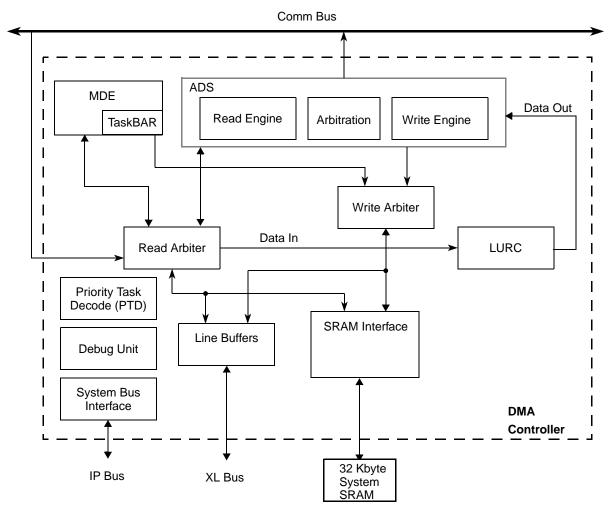

| 23.1  | Introducti  | ion                                           | 23-1  |

|       | 23.1.1      | Block Diagram                                 |       |

|       | 23.1.2      | Overview                                      |       |

|       | 23.1.3      | Features                                      |       |

| 23.2  |             | Signals                                       |       |

|       | 23.2.1      | DREQ[1:0]                                     |       |

|       | 23.2.2      | DACK[1:0]                                     |       |

| 23.3  |             | Map/Register Definitions                      |       |

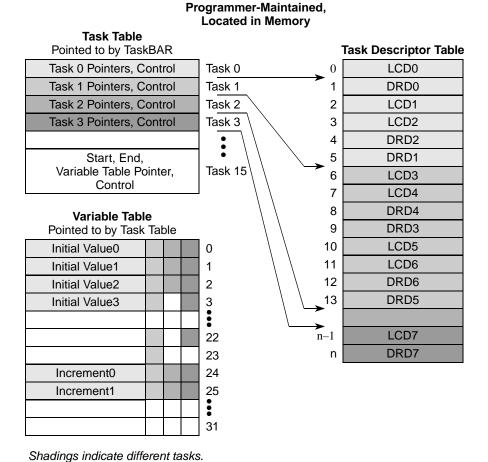

| 20.0  | 23.3.1      | DMA Task Memory                               |       |

|       | 23.3.2      | Memory Structure                              |       |

|       | 23.3.3      | DMA Registers                                 |       |

|       | <u> </u>    | 21111 1051010                                 |       |

|      | 23.3.4     | External Request Module Registers  |       |

|------|------------|------------------------------------|-------|

| 23.4 | Functiona  | al Description                     |       |

|      | 23.4.1     | Tasks                              |       |

|      | 23.4.2     | Descriptors                        | 23-23 |

|      | 23.4.3     | Task Initialization                | 23-23 |

|      | 23.4.4     | Initiators                         | 23-23 |

|      | 23.4.5     | Prioritization                     | 23-24 |

|      | 23.4.6     | Context Switch                     | 23-24 |

|      | 23.4.7     | Data Movement                      | 23-24 |

|      | 23.4.8     | Data Manipulation                  |       |

|      | 23.4.9     | Line Buffers                       | 23-26 |

|      | 23.4.10    | Termination of Loop                | 23-27 |

|      | 23.4.11    | Interrupts                         | 23-27 |

|      |            | Debug Unit                         |       |

| 23.5 | Programm   | ning Model                         | 23-27 |

|      | 23.5.1     | Register Initialization            |       |

|      | 23.5.2     | Task Memory                        | 23-28 |

| 23.6 | Timing D   | viagrams                           |       |

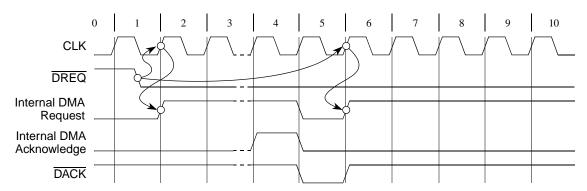

|      | 23.6.1     | Level-Triggered Requests           |       |

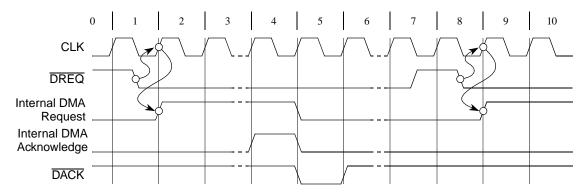

|      | 23.6.2     | Edge-Triggered Requests            |       |

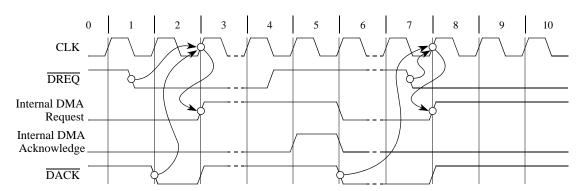

|      | 23.6.3     | Pipelined Requests                 | 23-31 |

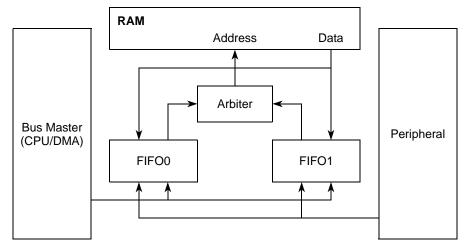

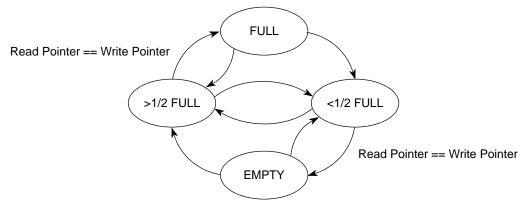

|      |            | Chapter 24                         |       |

|      |            | Chapter 24 Comm Bus FIFO Interface |       |

| 24.1 | Introducti | ion                                | 24-1  |

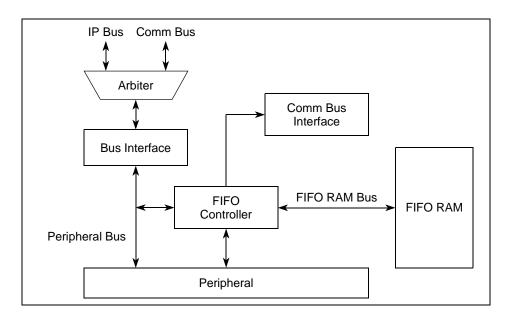

| 24.1 | 24.1.1     | Block Diagram                      |       |

|      | 24.1.2     | Overview                           |       |

|      | 24.1.3     | Features                           |       |

| 24.2 |            | Map/Register Definition            |       |

| 21.2 | 24.2.1     | FIFO Interface Registers           |       |

| 24 3 |            | al Description                     |       |

| 25   | 24.3.1     | Flow control                       |       |

|      | 24.3.2     | Wait Conditions                    |       |

|      | 24.3.3     | Error reporting                    |       |

|      | 24.3.4     | Debug Operation                    |       |

|      |            |                                    |       |

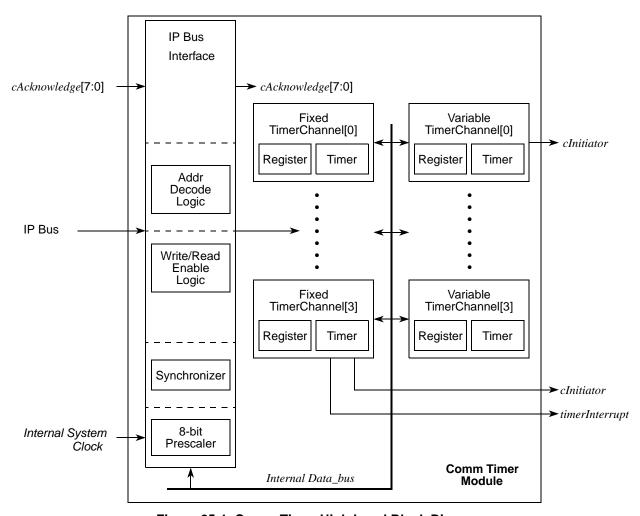

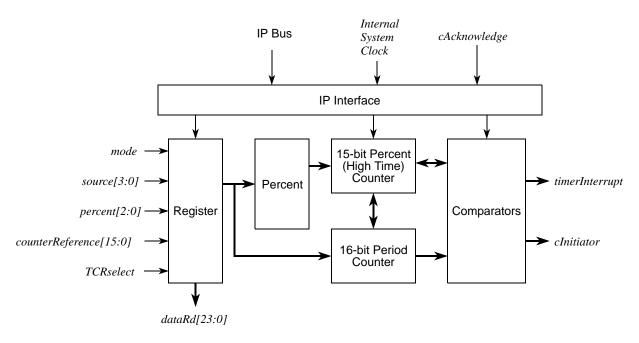

|      |            | Chapter 25                         |       |

|      |            | Comm Timer Module (CTM)            |       |

| 25.1 | Introduct  | ion                                |       |

|      | 25.1.1     | Block Diagrams                     |       |

|      | 25.1.2     | Overview                           |       |

| 25.2 |            | Signals                            |       |

|      | 25.2.1     | Comm Timer External Clock[7:0]     |       |

| 25.3 | •          | Map/Register Definition            |       |

|      | 25.3.1     | Timer Module Register Map          | 25-5  |

|      |            |                                    |       |

|      | 25.3.2    | Register Descriptions                                  | 25-5  |

|------|-----------|--------------------------------------------------------|-------|

| 25.4 | Function  | al Description                                         |       |

|      | 25.4.1    | Fixed and Variable Timers In Baud Clock Generator Mode |       |

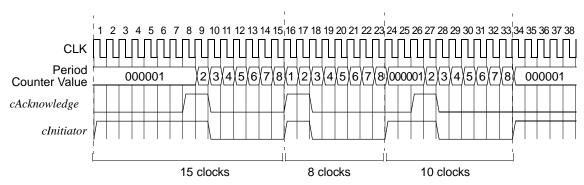

|      | 25.4.2    | Fixed Timer Channel in Task Initiator Mode             | 25-9  |

|      | 25.4.3    | Variable Timer Channel in Task Initiator Mode          | 25-11 |

|      |           | Chapter 26                                             |       |

|      |           | Programmable Serial Controller (PSC)                   |       |

| 26.1 | Introduct | tion                                                   | 26-1  |

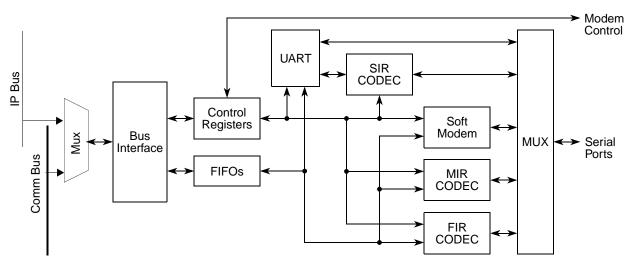

|      | 26.1.1    | Block Diagram                                          | 26-1  |

|      | 26.1.2    | Overview                                               | 26-1  |

|      | 26.1.3    | Features                                               | 26-1  |

|      | 26.1.4    | Modes of Operation                                     | 26-1  |

| 26.2 | Signal D  | escription                                             | 26-2  |

|      | 26.2.1    | PSCnCTS/PSCBCLK                                        | 26-2  |

|      | 26.2.2    | PSCnRTS/PSCFSYNC                                       | 26-2  |

|      | 26.2.3    | PSCnrxd                                                | 26-2  |

|      | 26.2.4    | pscntxd                                                | 26-3  |

|      | 26.2.5    | Signal Properties in Each Mode                         |       |

| 26.3 | Memory    | Map/Register Definition                                |       |

|      | 26.3.1    | Overview                                               | 26-3  |

|      | 26.3.2    | Module Memory Map                                      |       |

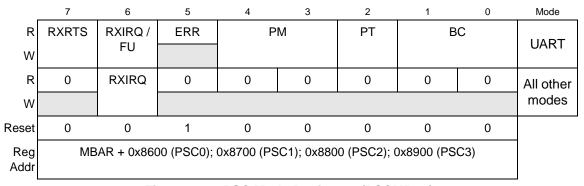

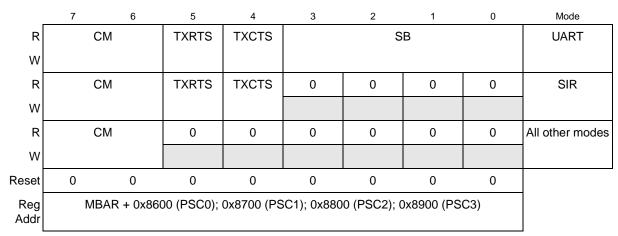

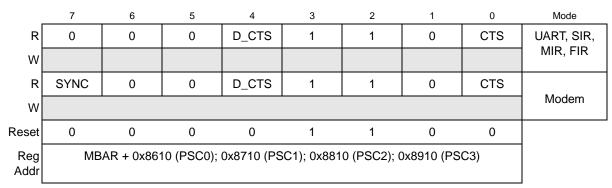

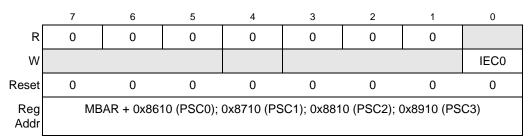

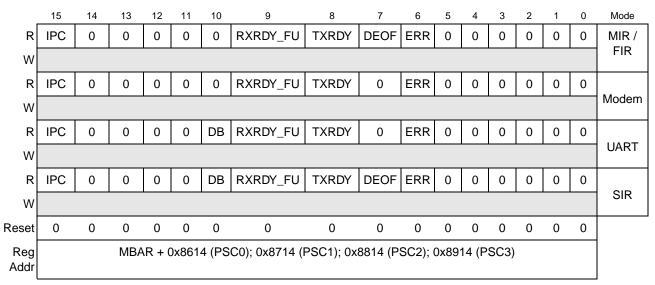

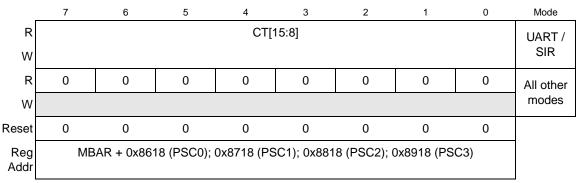

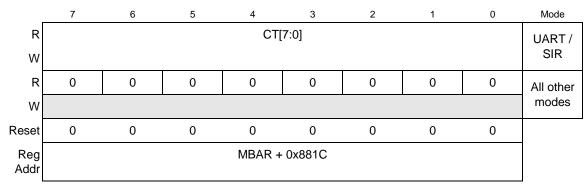

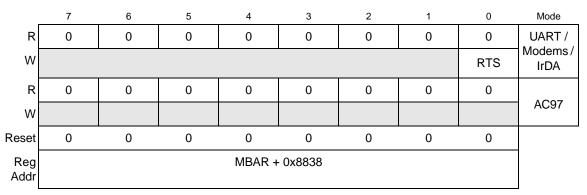

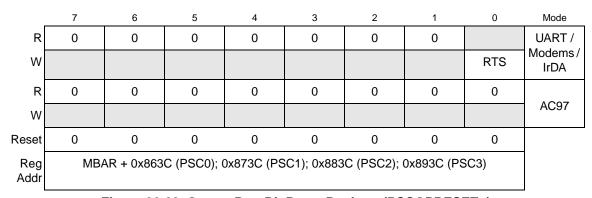

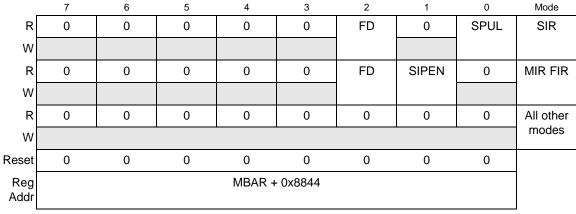

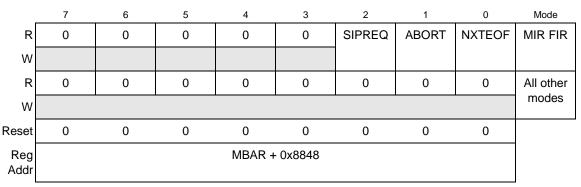

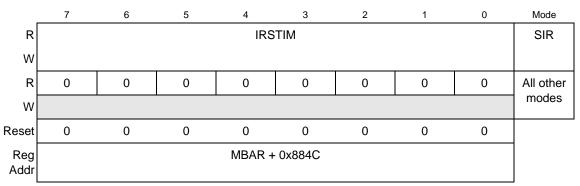

|      | 26.3.3    | Register Descriptions                                  | 26-5  |

| 26.4 | Function  | al Description                                         | 26-37 |

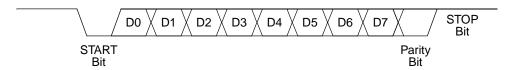

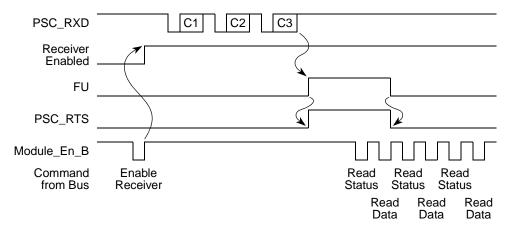

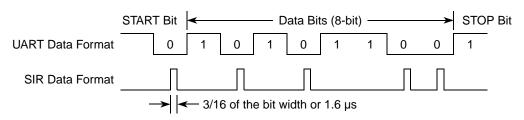

|      | 26.4.1    | UART Mode                                              |       |

|      | 26.4.2    | Multidrop Mode                                         |       |

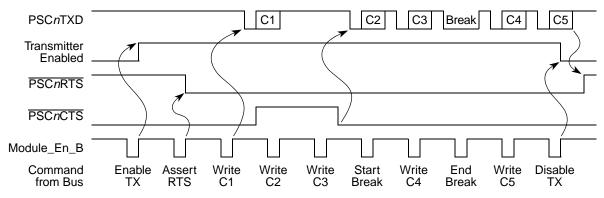

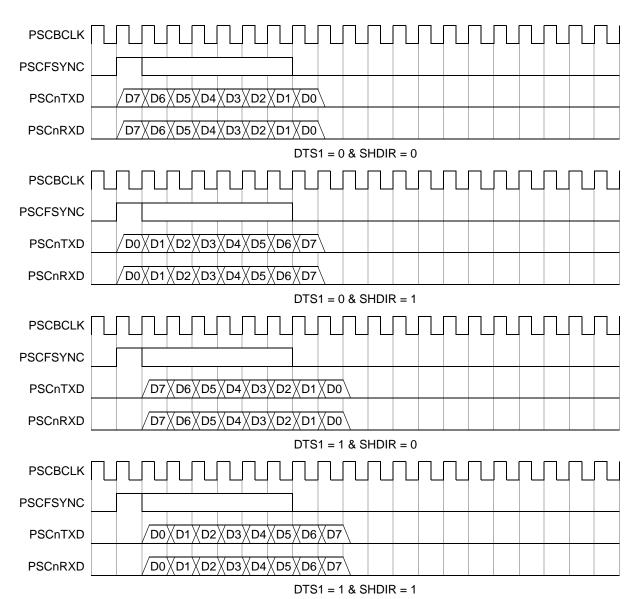

|      | 26.4.3    | Modem8 Mode                                            | 26-39 |

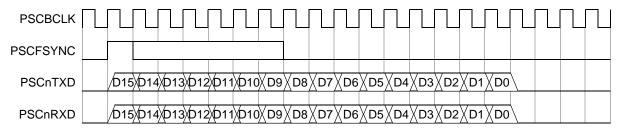

|      | 26.4.4    | Modem16 Mode                                           |       |

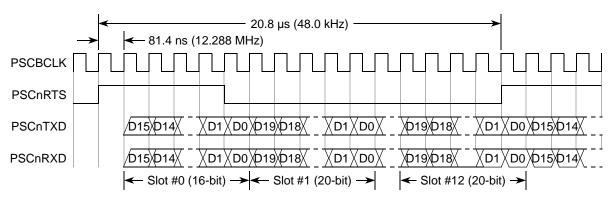

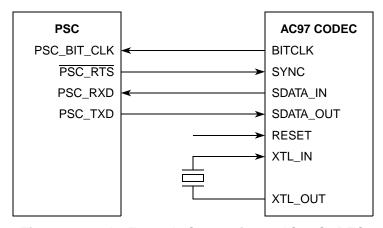

|      | 26.4.5    | AC97 Mode                                              |       |

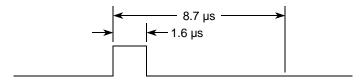

|      | 26.4.6    | SIR Mode                                               |       |

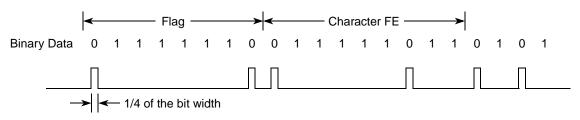

|      | 26.4.7    | MIR Mode                                               |       |

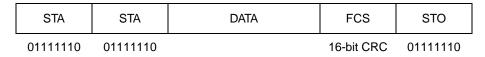

|      | 26.4.8    | FIR Mode                                               |       |

|      |           | PSC FIFO System                                        |       |

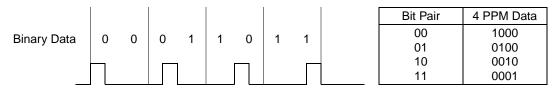

|      |           | Looping Modes                                          |       |

| 26.5 | Resets    |                                                        |       |

|      | 26.5.1    | General                                                |       |

|      | 26.5.2    | Description of Reset Operation                         |       |

| 26.6 | Interrupt | S                                                      |       |

|      | 26.6.1    | Description of Interrupt Operation                     |       |

| 26.7 | Software  | Environment                                            |       |

|      | 26.7.1    | General                                                |       |

|      | 26.7.2    | Configuration                                          | 26-51 |

|      | 26.7.3    | Programming                                            |       |

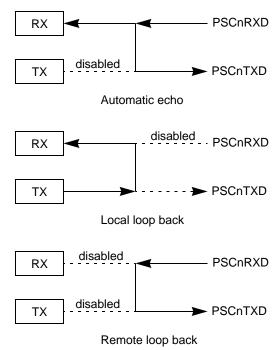

# Chapter 27 DMA Serial Peripheral Interface (DSPI)

| 27.1 | Overviev   | v                                                         | 27-1  |

|------|------------|-----------------------------------------------------------|-------|

| 27.2 | Features   |                                                           | 27-1  |

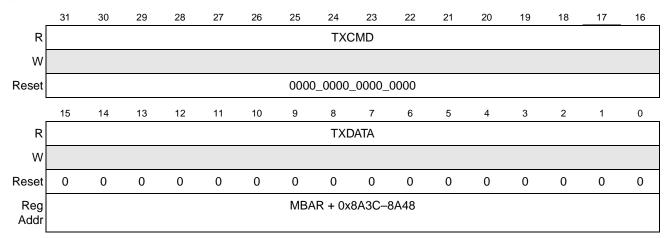

| 27.3 | Block Di   | agram                                                     | 27-2  |

| 27.4 | Modes of   | f Operation                                               | 27-2  |

|      | 27.4.1     | Master Mode                                               | 27-2  |

|      | 27.4.2     | Slave Mode                                                | 27-2  |

| 27.5 | Signal D   | escription                                                | 27-3  |

|      | 27.5.1     | Overview                                                  | 27-3  |

|      | 27.5.2     | Detailed Signal Descriptions                              | 27-3  |

| 27.6 | Memory     | Map and Registers                                         | 27-4  |

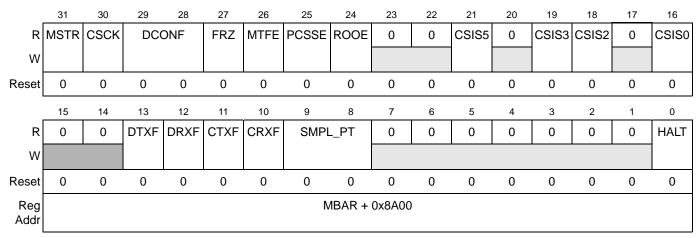

|      | 27.6.1     | DSPI Module Configuration Register (DMCR)                 | 27-5  |

|      | 27.6.2     | DSPI Transfer Count Register (DTCR)                       | 27-7  |

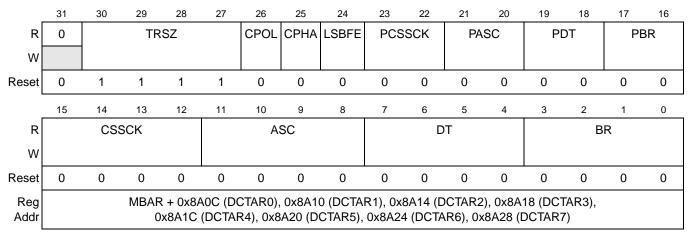

|      | 27.6.3     | DSPI Clock and Transfer Attributes Registers 0–7 (DCTARn) | 27-7  |

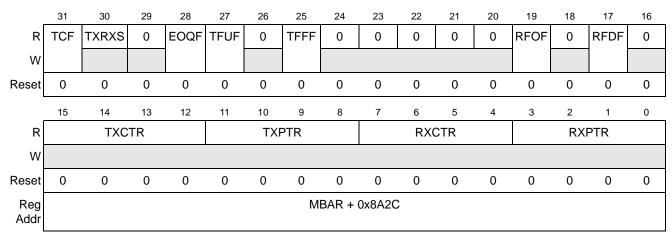

|      | 27.6.4     | DSPI Status Register (DSR)                                | 27-11 |

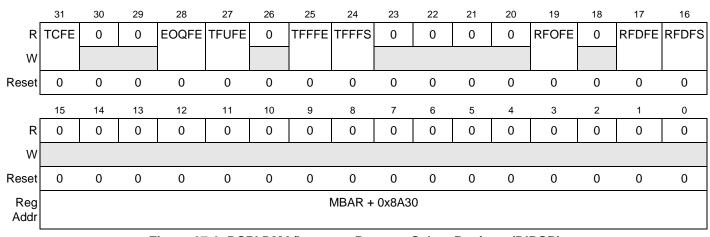

|      | 27.6.5     | DSPI DMA/Interrupt Request Select Register (DIRSR)        | 27-13 |

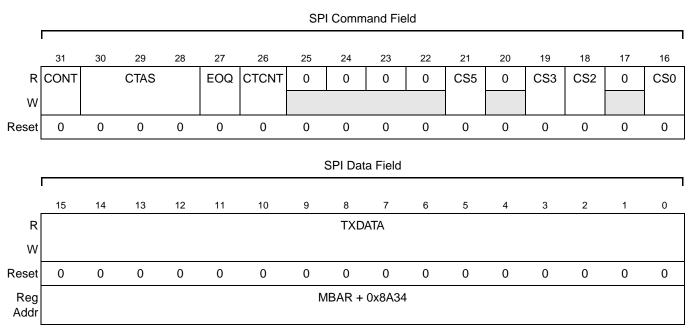

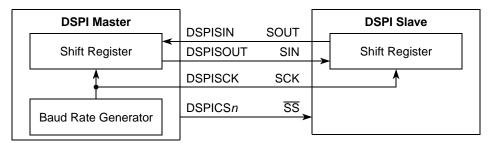

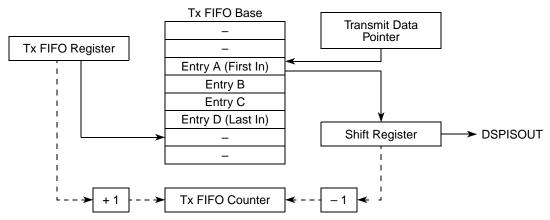

|      | 27.6.6     | DSPI Tx FIFO Register (DTFR)                              | 27-15 |

|      | 27.6.7     | DSPI Rx FIFO Register (DRFR)                              | 27-16 |

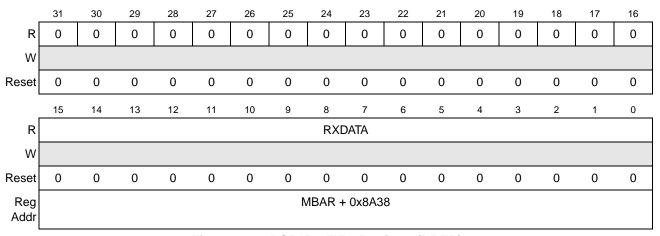

|      | 27.6.8     | DSPI Tx FIFO Debug Registers 0–3 (DTFDRn)                 | 27-17 |

|      | 27.6.9     | DSPI Rx FIFO Debug Registers 0–3 (DRFDRn)                 | 27-17 |

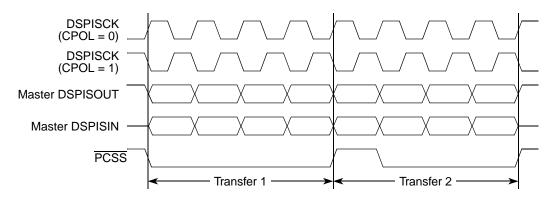

| 27.7 | Function   | al Description                                            | 27-18 |

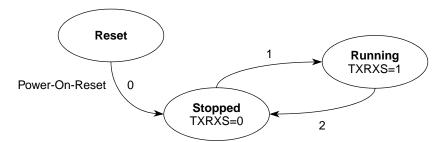

|      | 27.7.1     | Start and Stop of DSPI Transfers                          | 27-19 |

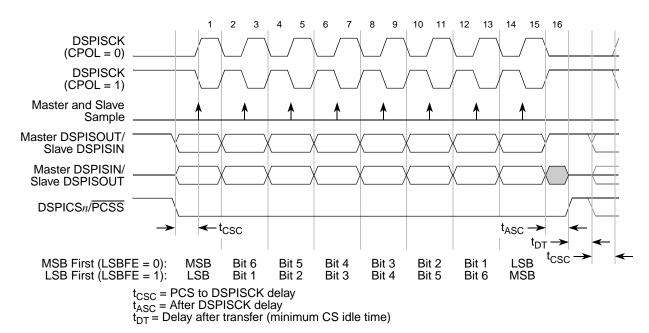

|      | 27.7.2     | Serial Peripheral Interface (SPI)                         | 27-20 |

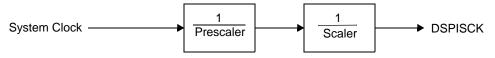

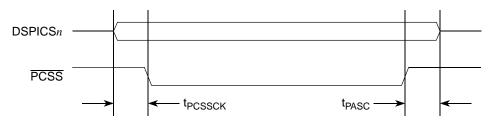

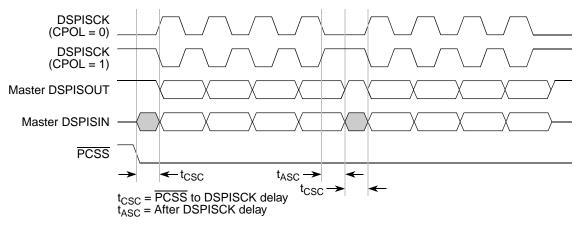

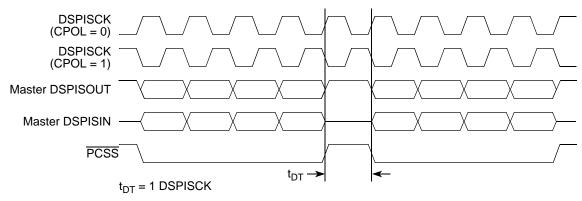

|      | 27.7.3     | DSPI Baud Rate and Clock Delay Generation                 | 27-22 |

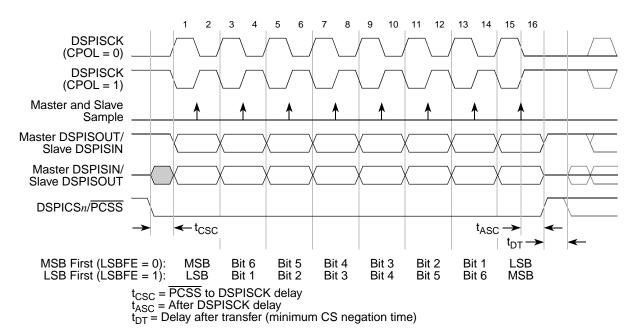

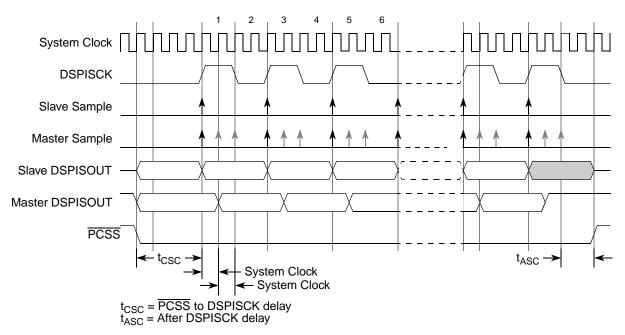

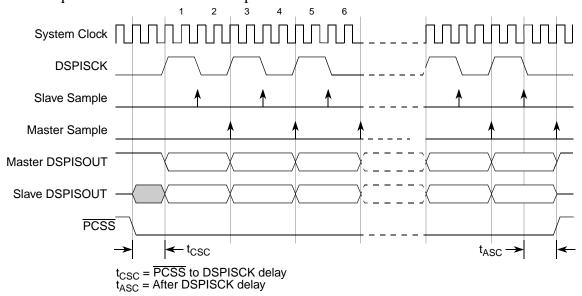

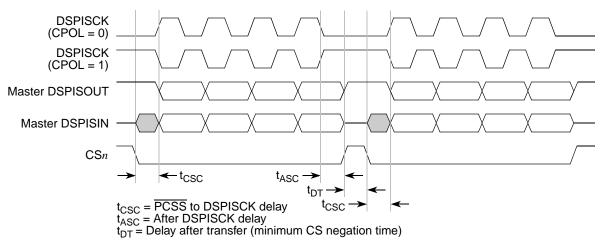

|      | 27.7.4     | Transfer Formats                                          |       |

|      | 27.7.5     | Continuous Serial Communications Clock                    | 27-30 |

|      | 27.7.6     | Interrupts/DMA Requests                                   | 27-31 |

| 27.8 | Initializa | tion and Application Information                          | 27-33 |

|      | 27.8.1     | How to Change Queues                                      | 27-33 |

|      | 27.8.2     | Baud Rate Settings                                        | 27-33 |

|      | 27.8.3     | Delay Settings                                            | 27-34 |

|      | 27.8.4     | Calculation of FIFO Pointer Addresses                     | 27-35 |

|      |            | 01 4 00                                                   |       |

|      |            | Chapter 28                                                |       |

| 20.1 | T . 1 .    | I <sup>2</sup> C Interface                                | 20.1  |

| 28.1 |            | ion                                                       |       |

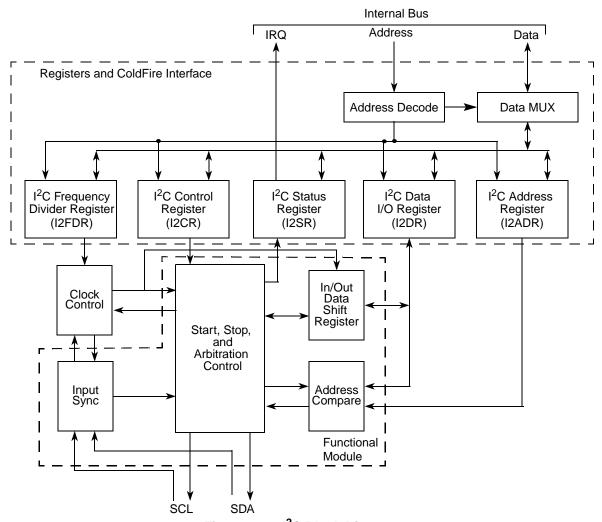

|      | 28.1.1     | Block Diagram                                             |       |

|      | 28.1.2     | I2C Overview                                              |       |

| 20.2 | 28.1.3     | Features                                                  |       |

|      |            | Signals                                                   |       |

| 28.3 | •          | Map/Register Definition                                   |       |

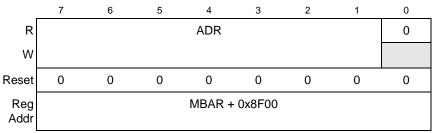

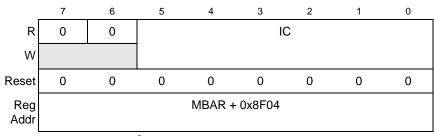

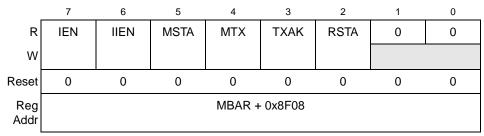

|      | 28.3.1     | I2C Register Map                                          |       |

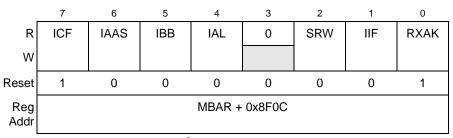

| 20.4 | 28.3.2     | Register Descriptions                                     |       |

| 28.4 | runction   | al Description                                            | 28-8  |

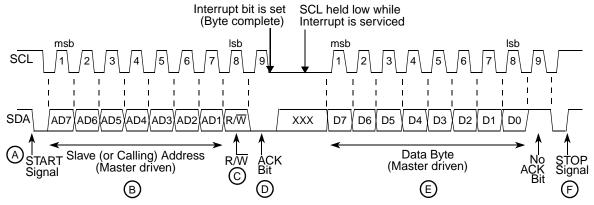

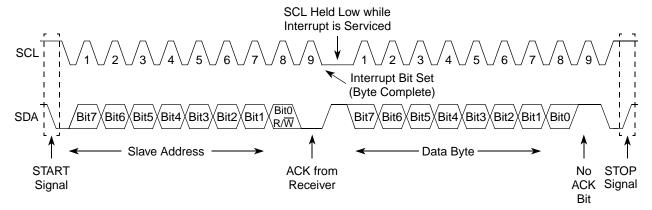

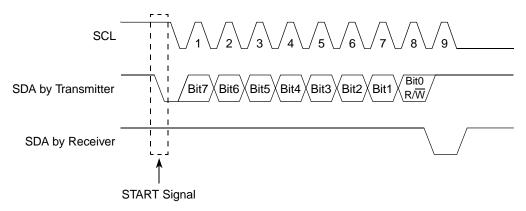

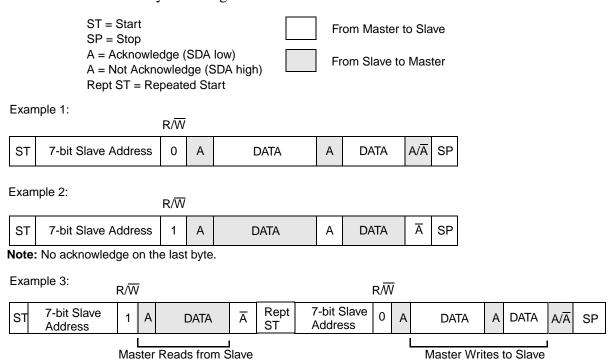

|       | 28.4.1     | START Signal                               | 28-9  |

|-------|------------|--------------------------------------------|-------|

|       | 28.4.2     | Slave Address Transmission                 | 28-9  |

|       | 28.4.3     | STOP Signal                                | 28-9  |

|       | 28.4.4     | Data Transfer                              | 28-9  |

|       | 28.4.5     | Acknowledge                                | 28-10 |

|       | 28.4.6     | Repeated Start                             |       |

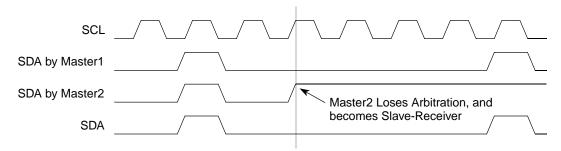

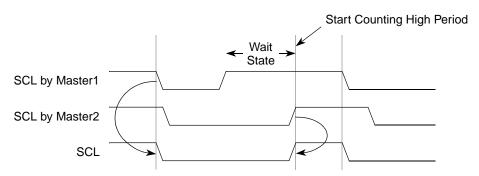

|       | 28.4.7     | Clock Synchronization and Arbitration      |       |

|       | 28.4.8     | Handshaking and Clock Stretching           | 28-12 |

| 28.5  | Initializa | tion Sequence                              | 28-12 |

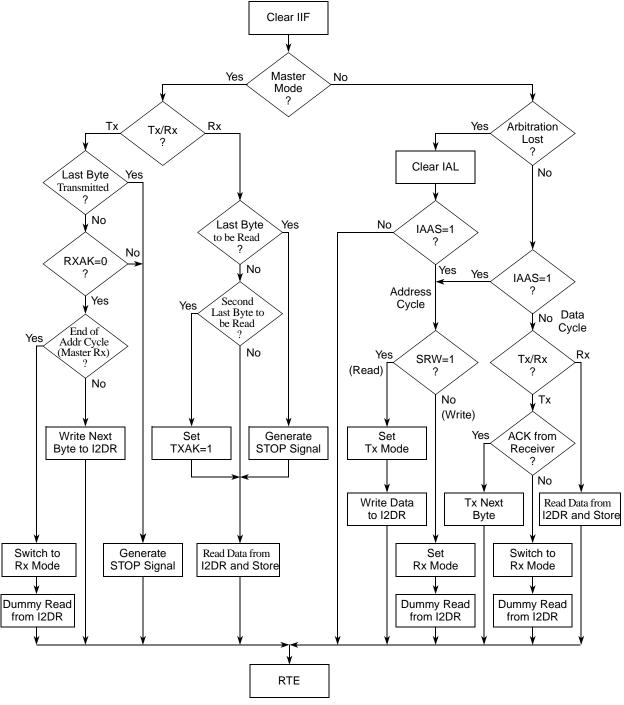

|       | 28.5.1     | Transfer Initiation and Interrupt          | 28-13 |

|       | 28.5.2     | Post-Transfer Software Response            | 28-14 |

|       | 28.5.3     | Generation of STOP                         | 28-15 |

|       | 28.5.4     | Generation of Repeated START               | 28-16 |

|       | 28.5.5     | Slave Mode                                 | 28-16 |

|       | 28.5.6     | Arbitration Lost                           | 28-18 |

|       | 28.5.7     | Flow Control                               | 28-18 |

|       |            |                                            |       |

|       |            | Chapter 29                                 |       |

|       |            | USB 2.0 Device Controller                  |       |

| 29.1  | Introduct  | tion                                       |       |

|       | 29.1.1     | Overview                                   |       |

|       | 29.1.2     | Features                                   |       |

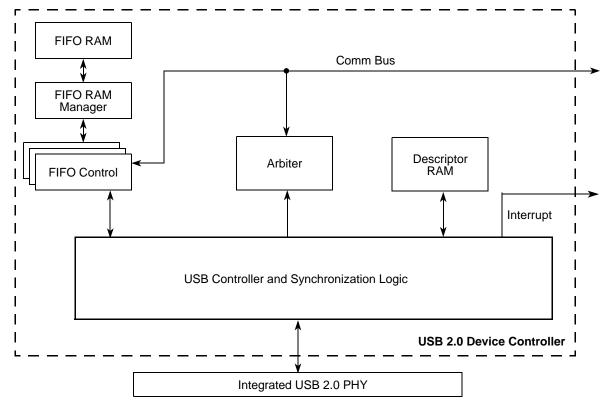

|       | 29.1.3     | Block Diagram                              |       |

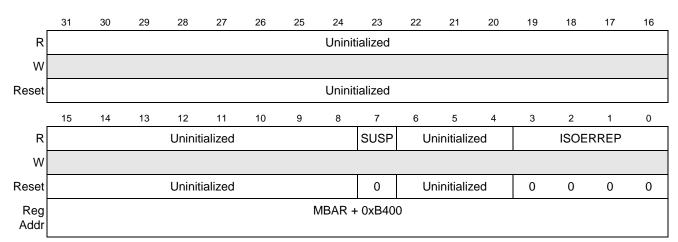

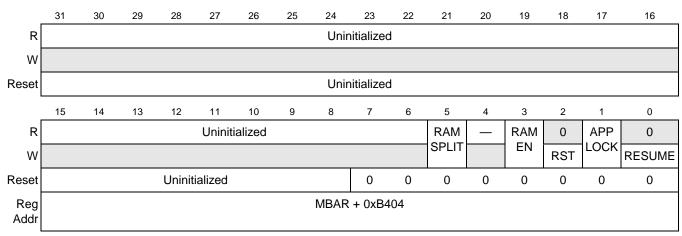

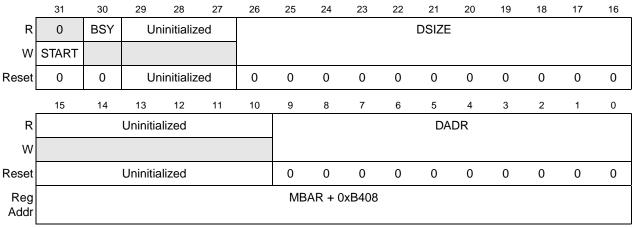

| 29.2  | •          | Map/Register Definition                    |       |

|       | 29.2.1     | USB Memory Map                             |       |

|       | 29.2.2     | USB Request, Control, and Status Registers |       |

|       | 29.2.3     | USB Counter Registers                      |       |

|       | 29.2.4     | Endpoint Context Registers                 |       |

| • • • | 29.2.5     | USB Endpoint FIFO Registers                |       |

| 29.3  |            | al Description                             |       |

|       | 29.3.1     | Interrupts                                 |       |

|       | 29.3.2     | Device Initialization                      |       |

|       |            | Exception Handling                         |       |

|       | 29.3.4     | Data Transfer Operations                   | 29-50 |

|       |            | Chapter 30                                 |       |

|       |            | Fast Ethernet Controller (FEC)             |       |

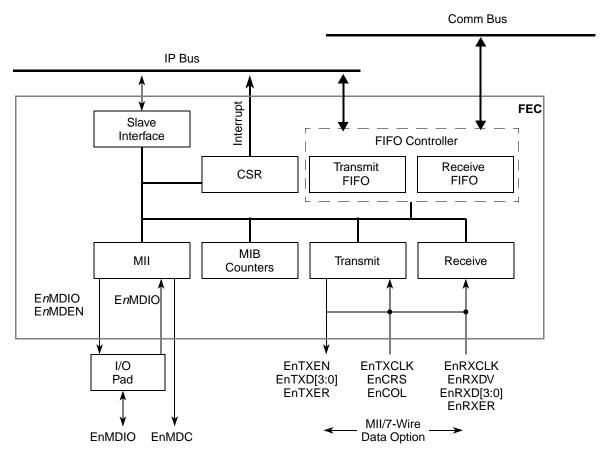

| 30.1  | Introduct  | tion                                       | 30.1  |

| 50.1  | 30.1.1     | MCF547x Family Products                    |       |

|       | 30.1.1     | Block Diagram                              |       |

|       | 30.1.2     | Overview                                   |       |

|       | 30.1.3     | Features                                   |       |

|       | 30.1.4     | Modes of Operation                         |       |

| 30.2  |            | Signals                                    |       |

| 50.2  | 30.2.1     | Transmit Clock (EnTXCLK)                   |       |

|       | 50.2.1     | Trunsmit Clock (Dill'ACDIX)                |       |

|      | 30.2.2    | Receive Clock (EnRXCLK)                        | 30-4  |

|------|-----------|------------------------------------------------|-------|

|      | 30.2.3    | Transmit Enable (EnTXEN)                       | 30-4  |

|      | 30.2.4    | Transmit Data[3:0] (EnTXD[3:0])                | 30-4  |

|      | 30.2.5    | Transmit Error (EnTXER)                        | 30-5  |

|      | 30.2.6    | Receive Data Valid (EnRXDV)                    | 30-5  |

|      | 30.2.7    | Receive Data[3:0] (EnRXD[3:0])                 | 30-5  |

|      | 30.2.8    | Receive Error (EnRXER)                         | 30-5  |

|      | 30.2.9    | Carrier Sense (EnCRS)                          | 30-5  |

|      | 30.2.10   | Collision (EnCOL)                              | 30-5  |

|      | 30.2.11   | Management Data Clock (EnMDC)                  | 30-5  |

|      | 30.2.12   | Management Data (EnMDIO)                       | 30-5  |

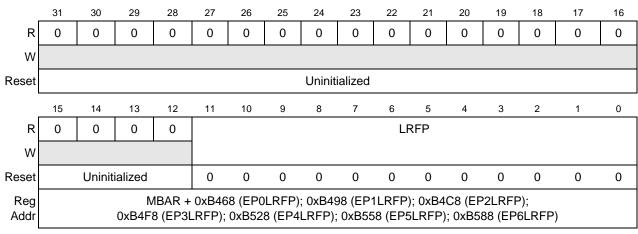

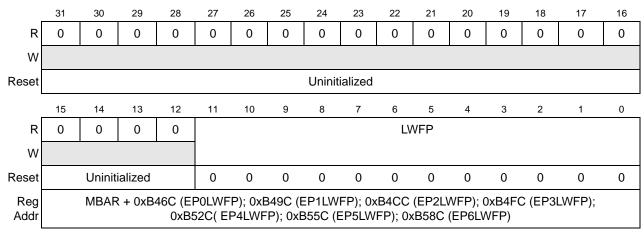

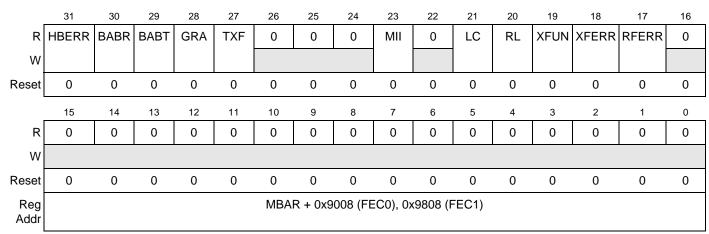

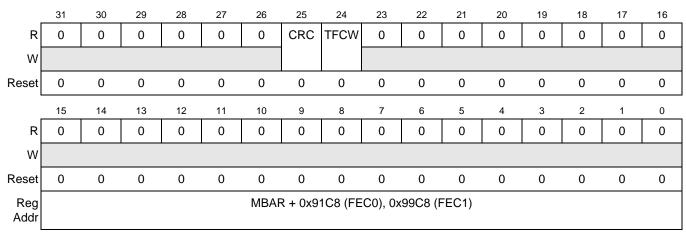

| 30.3 | Memory I  | Map/Register Definition                        | 30-6  |

|      | 30.3.1    | Top Level Module Memory Map                    | 30-6  |

|      | 30.3.2    | Detailed Memory Map (Control/Status Registers) |       |

|      | 30.3.3    | MIB Block Counters Memory Map                  | 30-8  |

| 30.4 | Functiona | l Description                                  |       |

|      | 30.4.1    | Initialization Sequence                        |       |

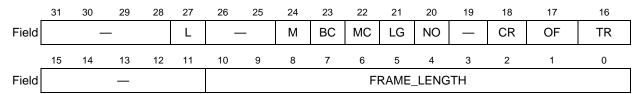

|      | 30.4.2    | Frame Control/Status Words                     |       |

|      | 30.4.3    | Network Interface Options                      |       |

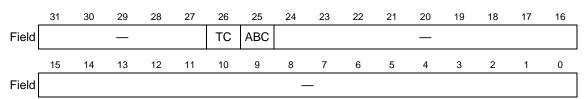

|      | 30.4.4    | FEC Frame Transmission                         |       |

|      | 30.4.5    | FEC Frame Reception                            |       |

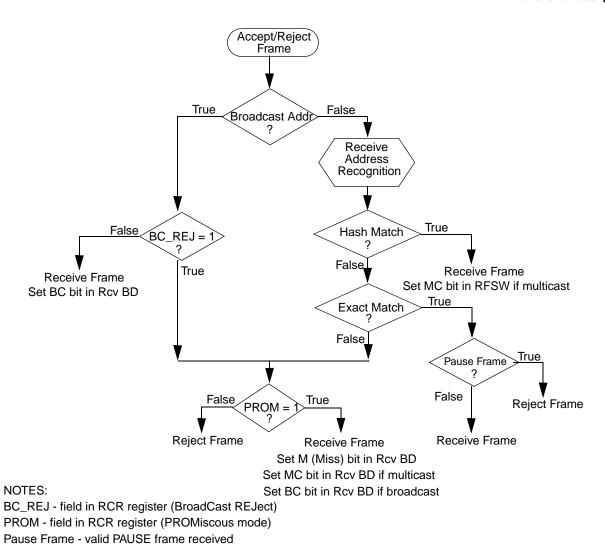

|      | 30.4.6    | Ethernet Address Recognition                   |       |

|      | 30.4.7    | Hash Algorithm                                 |       |

|      | 30.4.8    | Full Duplex Flow Control                       |       |

|      | 30.4.9    | Inter-Packet Gap (IPG) Time                    |       |

|      |           | Collision Handling                             |       |

|      |           | Internal and External Loopback                 |       |

|      |           | Ethernet Error-Handling Procedure              |       |

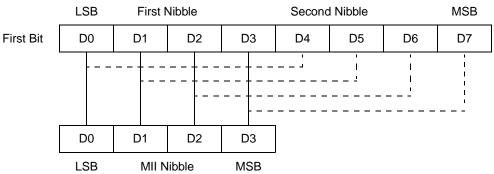

|      |           | MII Data Frame                                 |       |

|      | 30.4.14   | MII Management Frame Structure                 | 30-56 |

|      |           | Chapter 21                                     |       |

|      |           | Chapter 31  Mechanical Data                    |       |

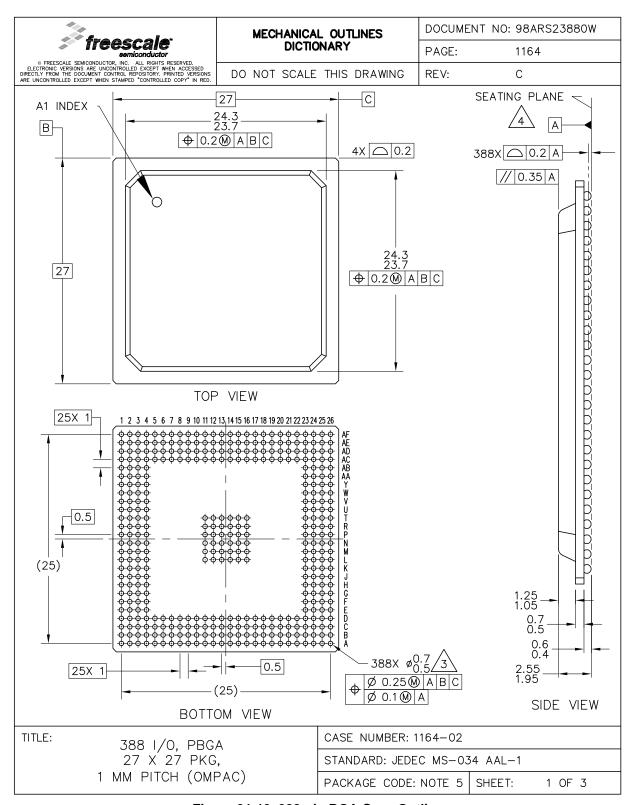

| 31.1 | Package   | Data                                           | 31_1  |

|      |           |                                                |       |

|      |           | al Diagrams                                    |       |

| J1.J | 31.3.1    | MCF5475/5474 Mechanical Diagram                |       |

|      |           | MCF5473/5474 Mechanical Diagram                |       |

| 31 4 |           | 1/5470 Mechanical Diagram                      |       |

|      |           | als 388-pin PBGA Package Outline               |       |

| 51.5 | Modiume   | and too pin 1 Doi 1 acrage outline             | 51 17 |

|      |           |                                                |       |

# Appendix A MCF547x Memory Map

xxii Freescale Semiconductor

#### **About This Book**

The primary objective of this reference manual is to define the functionality of the MCF547x processors for use by software and hardware developers.

The information in this book is subject to change without notice, as described in the disclaimers on the title page of this book. As with any technical documentation, it is the readers' responsibility to be sure they are using the most recent version of the documentation.

To locate any published errata or updates for this document, refer to the world-wide web at http://www.freescale.com/coldfire.

#### **Audience**

This manual is intended for system software and hardware developers and applications programmers who want to develop products for the MCF547x. It is assumed that the reader understands operating systems, microprocessor system design, basic principles of software and hardware, and basic details of the ColdFire architecture.

#### Organization

Following is a summary and a brief description of the major sections of this manual:

- Chapter 1, "Overview," includes general descriptions of the modules and features incorporated in the MCF547x, focussing in particular on new features.

- Chapter 2, "Signal Descriptions," provides an alphabetical listing of MCF547x signals, including which are inputs or outputs, how they are multiplexed, and the state of each signal at reset.

- Part I, "Processor Core," is intended for system designers who need to understand the operation of the MCF547x ColdFire core and its enhanced multiply/accumulate (EMAC) execution unit. It describes the programming and exception models, Harvard memory implementation, and debug module. Part 1 contains the following chapters:

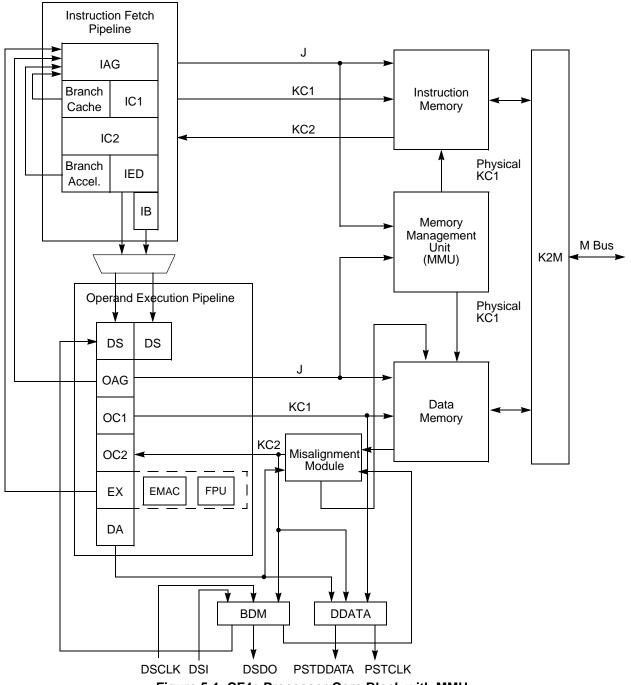

- Chapter 3, "ColdFire Core," provides an overview of the microprocessor core of the MCF547x. The chapter begins with a description of enhancements from the V3 ColdFire core, and then fully describes the V4e programming model as it is implemented on the MCF547x. It also includes a full description of exception handling, data formats, an instruction set summary, and a table of instruction timings.

- Chapter 4, "Enhanced Multiply-Accumulate Unit (EMAC)," describes the MCF547x enhanced multiply/accumulate unit, which executes integer multiply, multiply-accumulate, and miscellaneous register instructions. The EMAC is integrated into the operand execution pipeline (OEP).