# Features

- 300 mA/1.9V/2.5V DC to DC for Co-processor Core

- 80 mA/2.8V Dual-mode LDO for Memories (LDO1)

- 130 mA/2.7V/2.8V LDO for Camera Module (LDO2)

- 130 mA/2.8V LDO for Analog Section Supply of Audio Stereo Codec (LDO6)

- 10 mA/1.8V/2.8V LDO for Digital Section Supply of Audio Stereo Codec (LDO7)

- 130 mA/2.8V LDO for Analog Section Supply of Bluetooth® Module (LDO4)

- 130 mA/2.8V LDO for Digital Section Supply of Bluetooth<sup>®</sup> Module (LDO5)

- 2 mA/2.4V/2.7V LDO for Low-power Device Control (LDO3)

- Open Drain Switch

- Three-channel Level Shifters

- LED Driver

- 0.5 mA/1.5V Bufferized Voltage Reference

- Power Management Start-up Controller and Reset Generation

- Over- and Under-voltage Protections

- Over-temperature Protection

- Shutdown, Sleep and Enable Modes

- Straightforward and Easy Interfacing to any Baseband Controller

- Small 5 mm x 5 mm, 49-ball BGA Package

## Description

The AT73C204 device provides an integrated power management solution for the addon multimedia features in new-generation mobile phones. These features include a camera module, sound system for polyphonic ringing tones, memory module for downloaded MP3 files, Bluetooth module for cordless headset, etc. The most common approach to the IC architecture of these new-generation mobile phones is a baseband processor for the basic telephony functions and a separate co-processor for the multimedia features. Atmel proposes the AT73C202 for power management of the baseband processor and RF elements, and the AT73C204 for power management of the multimedia features.

The AT73C204 is suitable for any telecommunications standard: GSM/GPRS, PDS, CDMA, CDMA2000, WCDMA or UMTS. It is packaged in a small form-factor 49-ball 5 mm x 5 mm BGA package.

Power Management for Mobiles (PM)

# AT73C204

6014A-PMGMT-10/03

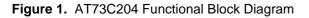

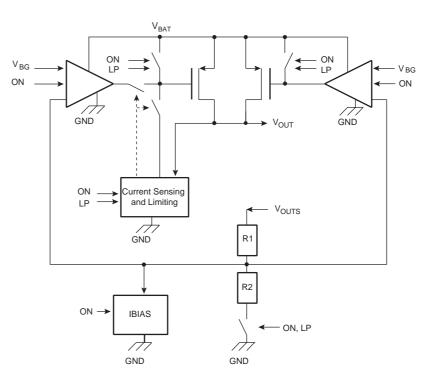

# **Functional Block Diagram**

AT73C204

2

# **Pin Description**

Table 1.

AT73C204 Pin Description

| Signal | Ball | Туре           | Description                       |

|--------|------|----------------|-----------------------------------|

| LEDI   | C1   | I              | LED driver input                  |

| LEDO   | C2   | 0              | LED driver output                 |

| VINF   | E1   | Power Supply   | Input voltage                     |

|        |      | Powe           | r On Block                        |

| CE     | D5   | I              | Chip Enable                       |

| GNDF   | C6   | Ground         | Ground                            |

| RES-B  | F6   | 0              | Reset open collector output       |

| GNDG   | E5   | Ground         | Ground                            |

|        |      | Baseban        | d Supply Block                    |

| VINA   | G6   | Power Supply   | Input supply for DC-DC converter  |

| LX     | F7   | 0              | DC-DC converter Output Inductor   |

| DM     | G5   | I              | Low-power/Full-power selector     |

| VOUTO  | G4   | 0              | DC-DC converter output            |

| GNDA   | G7   | Ground         | Ground of DC-DC Converter         |

| VINB   | A5   |                | Input supply for LDO1, LDO2, LDO3 |

| EN2    | B5   | I              | Enable LDO2                       |

| VOUT2  | B4   | 0              | LDO2 output voltage               |

| GNDB   | A7   | Ground         | Ground for LDO1, LDO2, LDO3       |

| VOUT1  | B6   | 0              | LDO1 output voltage               |

| VREF   | B7   | 0              | Bufferized voltage reference      |

| VOUT3  | A6   | 0              | LDO3 output voltage               |

|        |      | RF Su          | upply Block                       |

| VINC   | A3   | Power Supply   | Input supply for LDO4, LDO5       |

| EN4    | B2   | I              | Enable LDO4                       |

| EN5    | C4   | I              | Enable LDO5                       |

| VOUT4  | B1   | 0              | LDO4 output voltage               |

| GNDC   | A2   | Ground         | Ground for LDO4, LDO5             |

| VOUT5  | A1   | 0              | LDO5 output voltage               |

|        |      | Vibrator and I | Buzzer Driver Block               |

| VIND   | D7   | Power Supply   | LDO6 input supply                 |

| EN6    | E6   | I              | Enable LDO6                       |

| VOUT6  | E7   | 0              | LDO6 output voltage               |

| SWI    | C5   | I              | Open drain enable                 |

| SWO    | B3   | 0              | Open drain output                 |

### Table 1. AT73C204 Pin Description (Continued)

| Signal | Ball | Туре         | Description                                |

|--------|------|--------------|--------------------------------------------|

| GNDD   | A4   | Ground       | Open drain ground                          |

|        |      | SIM Int      | terface Block                              |

| VINE   | G1   | Power Supply | LDO7 input supply                          |

| EN7    | G3   | I            | Enable LDO7                                |

| DVB    | F4   | I            | Dual-voltage setting on LDO7               |

| LSI1   | E4   | I            | Channel 1 level shifter input              |

| LSI2   | F3   | I            | Channel 2 level shifter input              |

| LSI3   | G2   | IO           | Channel 3 level shifter input              |

| VOUT7  | E3   | 0            | LDO7 output voltage                        |

| LSO1   | F1   | 0            | Channel 1 level shifter output             |

| LSO2   | F2   | 0            | Channel 2 level shifter output             |

| LSO3   | E2   | IO           | Channel 3 level shifter output             |

|        |      | Miso         | cellaneous                                 |

| CREF   | C7   | IO           | Band gap decoupling                        |

| GNDE   | D1   | Ground       | Digital ground                             |

| DVA    | D4   | I            | Dual-voltage setting for DC-DC, LDO2, LDO3 |

| NC     | D2   |              |                                            |

| NC     | D3   |              |                                            |

| NC     | C3   |              |                                            |

| NC     | D6   |              |                                            |

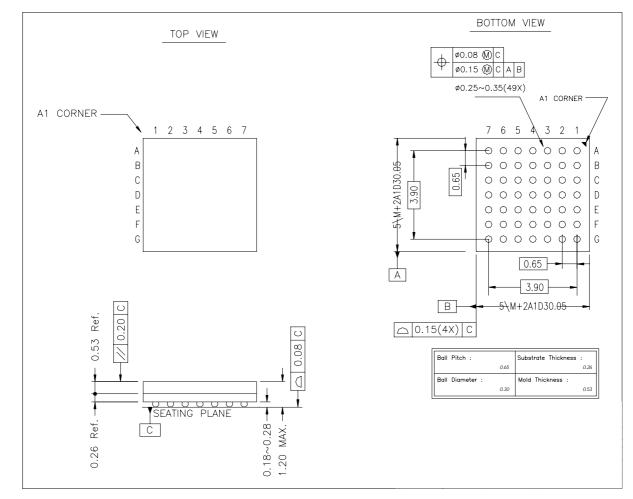

Figure 2. AT73C204 Pin Configuration in 49-ball BGA Package

|   |           | 1           | 2          | 3          | 4          | 5        | 6           | 7           |

|---|-----------|-------------|------------|------------|------------|----------|-------------|-------------|

|   | $\square$ |             |            |            |            |          |             |             |

| A |           | ()<br>VOUT5 |            |            |            |          | ()<br>VOUT3 |             |

| В |           |             |            |            |            |          | ()<br>VOUT1 |             |

| С |           | )<br>LEDI   | ()<br>LED0 |            | ()<br>EN5  |          | ()<br>GNDF  |             |

| D |           | -           | ()<br>NC   |            | ()<br>DVA  |          | ()<br>NC    | ()<br>VIND  |

| Е |           | ()<br>VINF  | ()<br>LSO3 | -          | ()<br>LSI1 | -        | ()<br>EN6   | ()<br>VOUT6 |

| F |           | ()<br>LSO1  |            | ()<br>LSI2 |            | -        | ()<br>RESB  | ()<br>LX    |

| G |           | ()<br>VINE  | -          | ()<br>EN7  | <<br>VOUT0 | ()<br>DM | -           | ()<br>GNDA  |

|   |           |             |            |            |            |          |             |             |

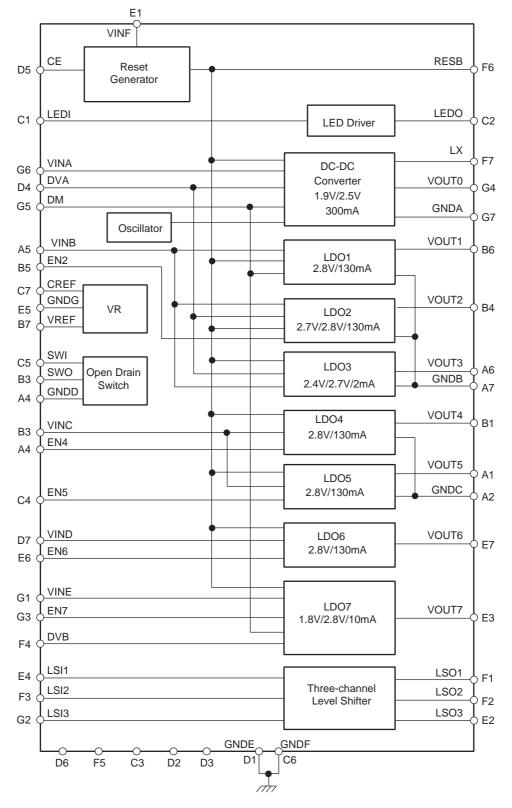

# **Application Schematic**

Figure 3. AT73C204 Application Schematic

# **External Components Specifications**

Table 2. External Component Specifications

| Symbol                     | Parameters                  |

|----------------------------|-----------------------------|

| R1                         | 4.7 kΩ, 1/8 W, 0603         |

| C1, C3, C4, C5, C6, C7, C8 | 2.2 μF - X5R 6.3V/10%, 0603 |

| C2                         | 22 µF Tantale R, TYPEA      |

| C9                         | 220 nF - X5R 10V/10%, 0603  |

| C10                        | 10 nF - X5R 10V/10%, 0402   |

| C11                        | 10 μF - X5R 6.3V/10%        |

| L1                         | 10 µH                       |

| D1                         | HSMH - C670                 |

6

## **Functional Description**

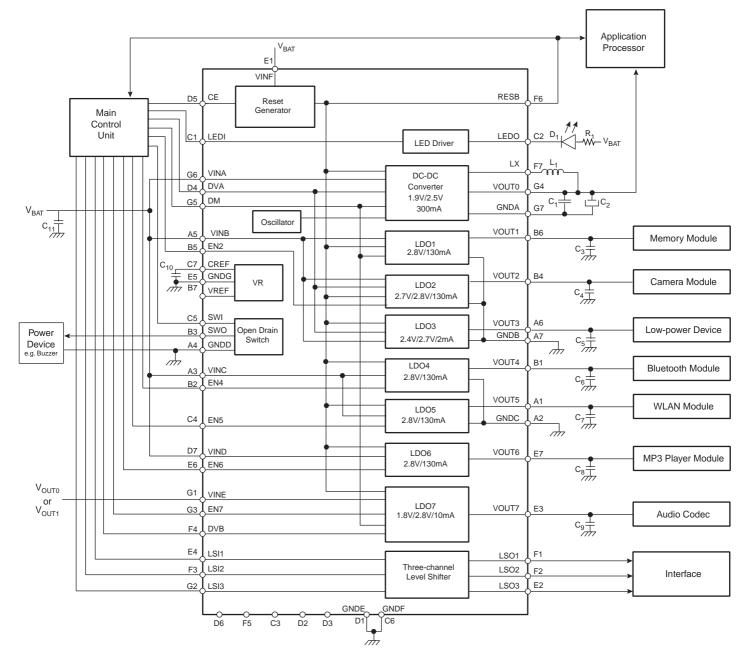

### 300 mA/1.9V/2.5V DC-to-DC Converter for Co-processor Core

This DC-to-DC converter is a synchronous mode DC-to-DC "buck"-switched regulator using fixed- frequency architecture (PWM) and capable of providing 300 mA of continuous current. It has two levels of voltage programming for the co-processor core (1.9V or 2.5V). The operating supply range is from 3.1V to 4.2V, making it suitable for Li-Ion, Lipolymer or Ni-MH battery applications. This DC-to-DC converter is based on the pulse width modulation architecture to control the noise perturbation for switching noise sensitive applications (GSM). The operating frequency is set to 900 KHz using an internal clock, allowing the use of small surface inductor and moderate output voltage ripple. The controller consists of a reference ramp generator, a feedback comparator, the logic driver used to drive the internal switches, the feedback circuits used to manage the different modes of operation and the over-current protection circuits. An economic mode has been defined to reduce quiescent current. A low-dropout voltage regulator in parallel to the DC-to-DC converter minimizes standby current consumption during standby mode.

#### Figure 4. Dual-power DC-to-DC Converter

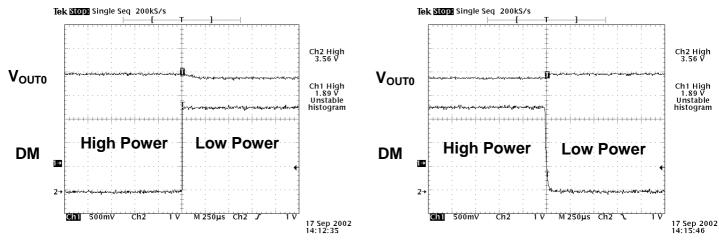

Low undershoot voltage is expected when going from PWM to LDO mode and viceversa. The circuit is designed in order to avoid any spikes when transition between two modes is enabled.

Figure 5. Low-power/Full-power DC-to-DC Converter Transition

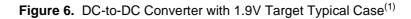

Figure 6 shows typical efficiency levels of the DC-to-DC converter for several input voltages.

Note: 1. L = 10  $\mu$ H, ESR = 0.2 Ohm, c = 22  $\mu$ F, @ESR = 0.1 Ohm

## LDO1, LDO3, LDO4, LDO5

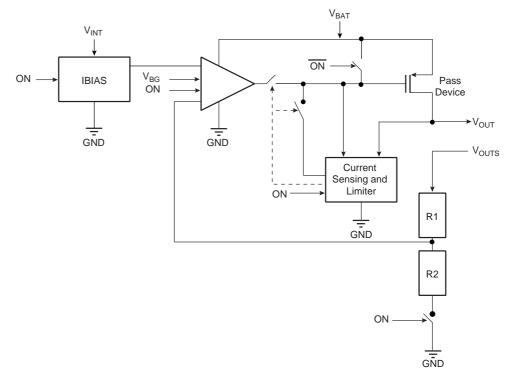

The PSRR measures the degree of immunization against voltage fluctuations achieved by a regulator. An example of its importance is in the case of a GSM phone when the antenna switch activates the RF power amplifier (PA). This causes a current peak of up to 2A on the battery, with an important spike on the battery voltage. The voltage regulator must filter or attenuate this spike.

AT73C204

8

# AT73C204

Figure 8 shows the Power Supply Rejection Ratio as functions of frequency and battery voltage. If a noise signal occurs at 1 kHz when the battery voltage is at 3V, the noise will be attenuated by 70 dB (divided by more than 3000) at the output of the regulator. Consequently, a 2V spike on the battery is attenuated to less than 1 mV, which is low enough to avoid any risk of malfunction by a device supplied by the regulator.

#### Figure 8. Power Supply Rejection Ratio in Function of Frequency and Battery Voltage

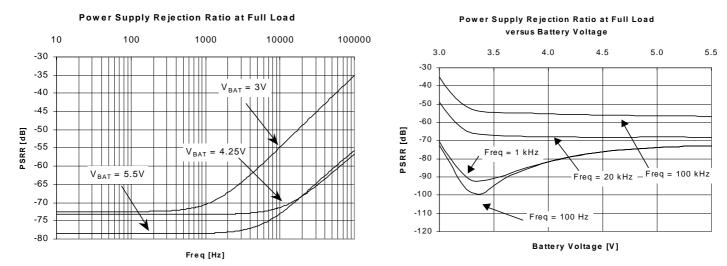

### LDO2, LDO6

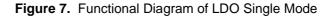

The first approach to reducing standby current is to decrease the standby current inside the regulators themselves. Atmel achieves this by implementing a dual mode architecture where two output transistors are used in parallel as switches in the regulation loop. Figure 9 illustrates this architecture.

|                                 | In Figure 9, the left-hand output transistor is sized large enough for the required output current under full load, for example, 100 mA. In order to achieve a sufficient margin of stability, the current sensing block uses a bias cell where the current consumption is linked to the required output current. The higher the output current, the higher the bias current needed to stabilize the loop. |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | The right-hand output transistor delivers a very small output current, typically less than 1 mA, sufficient only to maintain the output voltage with enough current to cover the leak-<br>age current of the supplied device. This requires a much smaller bias current and, consequently, a smaller standby current inside the regulator.                                                                 |

| LDO7                            | This regulator has extremely low quiescent current and is suited where power supply is enabled almost all the time. Typical use could be the supply of back-up battery.                                                                                                                                                                                                                                    |

| Temperature Sensor              | The temperature sensor voltage output is a linear function of temperature.                                                                                                                                                                                                                                                                                                                                 |

|                                 | The temperature seen by the sensor is directly related to the chip activity and the power internally dissipated. To get a good indication of the ambient temperature, the software must take into account this offset.                                                                                                                                                                                     |

| Three-channel Level<br>Shifters | This block provides a DC-to-DC or Memory Card level shifter and specific ESD protec-<br>tions. Signals are level-shifted on the LDO2 supply, allowing dual-voltage option: 1.8V<br>or 2.8V. If the memory type is Subscriber Identity Module (SIM) Card, level shifters are<br>compliant with ETSI GSM11.12 & 11.18.                                                                                       |

AMEI

## Absolute Maximum Ratings

| Operating Temperature (Industrial)40°C to +85°C                          | *NOTICE: Stresses beyond those listed under "Absolute |

|--------------------------------------------------------------------------|-------------------------------------------------------|

|                                                                          | Maximum Ratings" may cause permanent dam-             |

| Storage Temperature                                                      | age to the device. This is a stress rating only and   |

|                                                                          | functional operation of the device at these or other  |

| Power Supply Input                                                       | conditions beyond those indicated in the opera-       |

| V <sub>INA</sub> , V <sub>INB</sub> ,,V <sub>INF</sub> 0.3V to +6.5V     | tional sections of this specification is not implied. |

|                                                                          | Exposure to absolute maximum rating conditions        |

| I/O Input (all except to power supply0.3V to $V_{\text{MAX}}\text{+}0.3$ | for extended periods may affect device reliability.   |

# **Recommended Operating Conditions**

## Table 3. Recommended Operating Conditions

| Parameter             | Conditions                                              | Min | Maw | Unit |

|-----------------------|---------------------------------------------------------|-----|-----|------|

| Operating Temperature |                                                         | -20 | 85  | °C   |

| Power Supply Input    | V <sub>INA</sub> , V <sub>INB</sub> ,, V <sub>INF</sub> | 3.0 | 4.5 | V    |

# **Electrical Characteristics**

# V<sub>OUT0</sub>

Table 4.  $V_{OUT0}$  Electrical Characteristics

| Symbol                   | Parameter                 | Conditions                                                           | Min  | Тур  | Max  | Unit |

|--------------------------|---------------------------|----------------------------------------------------------------------|------|------|------|------|

| V <sub>INA</sub>         | Operating Supply Voltage  |                                                                      | 3    |      | 5.5  | V    |

| V <sub>OUT0</sub>        | Output Voltage            | Full-power<br>(DVA = 0, DM = 0)                                      | 1.80 | 1.90 | 2.0  | V    |

| V <sub>OUT0</sub>        | Output Voltage            | Full-power<br>(DVA = 1, DM = 0)                                      | 2.45 | 2.50 | 2.55 | V    |

| I <sub>OUT0</sub>        | Output Current            | Full-power<br>(DM = 0)                                               |      | 300  | 400  | mA   |

| ISD                      | Shutdown Current          |                                                                      |      | 0.1  | 1    | μΑ   |

| E <sub>FF</sub>          | Efficiency                | I <sub>OUT</sub> = 10 mA to 200 mA @1.9V                             |      | 90   |      | %    |

| $\Delta V_{\text{DCLD}}$ | Static Load Regulation    | Full-power Mode (10% to 90% of I <sub>OUT(MAX)</sub>                 |      | 50   |      | mV   |

| $\Delta V_{\text{TRLD}}$ | Transient Load Regulation | Full-power Mode (10% to 90% of $I_{OUT(MAX)}$ , $T_R = T_F = 5\mu s$ |      | 50   |      | mV   |

| $\Delta V_{\text{DCLE}}$ | Static Line Regulation    | Full-power Mode (10% to 90% of $I_{OUT(MAX)}$ , 3.2V to 4.2V)        |      | 20   |      | mV   |

| $\Delta V_{\text{TRLE}}$ | Transient Line Regulation | Full-power Mode (10% to 90% of $I_{OUT(MAX)}$ , 3.2V to 4.2V)        |      | 35   |      | mV   |

| V <sub>OUT0</sub>        | Output Voltage            | Low-power Mode<br>(DVA = 0, DM = 1)                                  | 1.75 | 1.85 | 1.95 | V    |

| V <sub>OUT0</sub>        | Output Voltage            | Low-power Mode<br>(DVA = 1, DM = 1)                                  | 2.35 | 2.40 | 2.45 | V    |

| I <sub>OUT0</sub>        | Output Current            | Low-power Mode (DM = 1)                                              |      |      | 10   | mA   |

| V <sub>DROP</sub>        | Dropout Voltage           | Low-power Mode (DM = 1)                                              |      |      | 400  | mV   |

| I <sub>QC</sub>          | Quiescent Current         | Low-power Mode (DM = 1)                                              |      | 11   | 14   | μA   |

| $\Delta V_{DCLD}$        | Static Load Regulation    | Low-power Mode (0 to 10 mA)                                          |      |      | 50   | mV   |

| $\Delta V_{\text{TRLD}}$ | Transient Load Regulation | Low-power Mode (0 to 10 mA),<br>$T_R = T_F = 5\mu s$                 |      |      | 10   | mV   |

| $\Delta V_{\text{DCLE}}$ | Static Line Regulation    | Low-power Mode (3.2V to 4.2V)                                        |      |      | 8    | mV   |

| $\Delta V_{\text{TRLE}}$ | transient Line Regulation | Low-power Mode (3.2V to 4.2V)                                        |      |      | 15   | mV   |

| PSRR                     | Ripple Rejection          | Low-power Mode up to 1 KHz                                           | 40   | 45   |      | dB   |

| $\Delta V_{LPFP}$        | Overshoot Voltage         | Voltage drop from Low-power to Full-power                            |      | 0    | 10   | mV   |

| $\Delta V_{\text{FPLP}}$ | Undershoot Voltage        | Voltage drop from Low-power to Full-power                            | -15  | 0    |      | mV   |

Table 5. LDO2 Electrical Characteristics

| Symbol             | Parameter                 | Conditions                                           | Min  | Тур  | Max  | Unit              |

|--------------------|---------------------------|------------------------------------------------------|------|------|------|-------------------|

| V <sub>INB</sub>   | Operating Supply Voltage  |                                                      | 3    |      | 5.5  | V                 |

| V <sub>OUT2</sub>  | Output Voltage            | DVA = 0                                              | 2.65 | 2.70 | 2.75 | V                 |

| V <sub>OUT2</sub>  | Output Voltage            | DVA = 1                                              | 2.75 | 2.80 | 2.85 | V                 |

| V <sub>INT</sub>   | Internal Supply Voltage   |                                                      | 2.4  |      | 2.6  | V                 |

| I <sub>OUT2</sub>  | Output Current            |                                                      |      | 80   | 130  | mA                |

| I <sub>QC</sub>    | Quiescent Current         |                                                      |      | 195  | 236  | μA                |

| DV <sub>OUT</sub>  | Line Regulation           | $V_{BAT}$ : 3V to 3.4V, $I_{OUT}$ = 130 mA           |      | 3    |      | mV                |

| DV <sub>PEAK</sub> | Line Regulation Transient | Same as above, $T_R = T_F = 5 \ \mu s$               |      | 4    |      | mV                |

| DV <sub>OUT</sub>  | Load Regulation           | 10% - 90% I <sub>OUT</sub> , V <sub>BAT</sub> = 3V   |      | 10   |      | mV                |

|                    |                           | 10% - 90%I <sub>OUT</sub> , V <sub>BAT</sub> = 5.0V  |      | 15   |      | mV                |

|                    |                           | 10% - 90% I <sub>OUT</sub> , V <sub>BAT</sub> = 5.5V |      | 15   |      | mV                |

| DV <sub>PEAK</sub> | Load Regulation Transient | Same as above, $T_R = T_F = 5 \ \mu s$               |      | 15   |      | mV                |

| PSRR               | Ripple rejection          | $F = 217Hz - V_{BAT} = 3.6V$                         |      | 70   |      | dB                |

| V <sub>N</sub>     | Output Noise              | BW: 10 Hz to 100 kHz                                 |      | 29   |      | μV <sub>RMS</sub> |

| T <sub>R</sub>     | Rise Time                 | 100% I <sub>OUT</sub> , 10% - 90% V <sub>OUT</sub>   |      |      | 50   | μs                |

| I <sub>SD</sub>    | Shut Down Current         |                                                      |      |      | 1    | μA                |

Table 6. LDO1 Electrical Characteristics

| Symbol             | Parameter                         | Conditions                                                                                               | Min  | Тур  | Max               | Unit          |

|--------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------|------|------|-------------------|---------------|

| V <sub>INB</sub>   | Operating Supply Voltage          |                                                                                                          | 3    |      | 5.5               | V             |

| V <sub>OUT1</sub>  | Output Voltage Full Power Mode    |                                                                                                          | 2.74 | 2.80 | 2.86              | V             |

| I <sub>OUT1</sub>  | Output Current Full Power Mode    |                                                                                                          |      | 50   | 80                | mA            |

| I <sub>OUT</sub>   | Output Current Low Power Mode     |                                                                                                          |      |      | 10                | mA            |

| I <sub>QC</sub>    | Quiescent Current FP Mode         |                                                                                                          | 25   | 30   | 36                | μA            |

| I <sub>QC</sub>    | Quiescent Current LP Mode         |                                                                                                          | 9.75 | 11.5 | 13.75             | μA            |

| DV <sub>OUT</sub>  | Line Regulation FP Mode           | $V_{BAT}$ : 3.4V to 3V, $I_{OUT}$ = 80 mA                                                                |      |      | 1                 | mV            |

| DV <sub>PEAK</sub> | Line Regulation Transient FP Mode | $V_{BAT}$ : from 5V to 5.4V and from 3.4V to 3V, $I_{OUT}$ = 80 mA, $T_R = T_F = 5 \ \mu s$              |      |      | 3                 | mV            |

| DV <sub>OUT</sub>  | Line Regulation LP Mode           | $V_{BAT}$ : 3.4V to 3V, $I_{OUT}$ = 5 mA                                                                 |      |      | 3                 | mV            |

| DV <sub>PEAK</sub> | Line Regulation Transient LP Mode | $V_{BAT}$ : from 5V to 5.4V and from 3.4V to 3V, $I_{OUT} = 5$ mA, $T_R = T_F = 5 \ \mu s$               |      |      | 4                 | mV            |

| DV <sub>OUT</sub>  | Load Regulation FP Mode           | From 0 to 80mA and from 90% to 10% $I_{OUT(MAX)}$ , $V_{BAT} = 3.4V$                                     |      |      | 3<br>(4 at 5.5V)  | mV            |

| DV <sub>PEAK</sub> | Load Regulation Transient FP Mode | From 0 to $I_{OUT(MAX)}$ and from 90% to 10% $I_{OUT(MAX)}$ , $T_R = T_F = 5 \ \mu s$ , $V_{BAT} = 3.4V$ |      |      | 23                | mV            |

| DV <sub>OUT</sub>  | Load Regulation LP Mode           | From 0 to 80mA and from 90% to 10% $I_{OUT(MAX)}$ , $V_{BAT} = 3.4V$                                     |      |      | 5<br>(10 at 5.5V) | mV            |

| PSRR               | Ripple Rejection                  | F = 217Hz                                                                                                | 40   | 45   |                   | dB            |

| V <sub>N</sub>     | Output Noise FP mode              | BW: 10 Hz to 100 kHz                                                                                     |      |      | 80                | $\mu V_{RMS}$ |

| V <sub>N</sub>     | Output Noise LP Mode              | BW: 10 Hz to 100 kHz                                                                                     |      |      | 300               | $\mu V_{RMS}$ |

| T <sub>R</sub>     | Rise Time FP                      | $I_{OUT} = I_{OUT(MAX)}$                                                                                 | 70   |      | 130               | μs            |

| T <sub>R</sub>     | Rise Time LP                      | $I_{OUT} = I_{OUT(MAX)}$                                                                                 | 50   |      | 170               | μs            |

| I <sub>SD</sub>    | Shut Down Current                 |                                                                                                          |      |      | 1                 | μA            |

| V <sub>BAT</sub>   | Operating Supply Voltage          |                                                                                                          | 3    |      | 5.5               | V             |

| V <sub>SAUV</sub>  | Internal Operating Supply Voltage |                                                                                                          | 2.74 | 2.8  | 2.86              | V             |

| I <sub>SC</sub>    | Short Circuit Current             |                                                                                                          |      | 50   | 80                | mA            |

Table 7. LDO3 Electrical Characteristics

| Symbol            | Parameter                | Conditions | Min  | Тур  | Max  | Unit |

|-------------------|--------------------------|------------|------|------|------|------|

| V <sub>INB</sub>  | Operating Supply Voltage |            | 3    |      | 5.5  | V    |

| V <sub>OUT3</sub> | Output Voltage           | BB1 = 0    | 2.4  | 2.45 | 2.50 | V    |

| V <sub>OUT3</sub> | Output Voltage           | BB1 = 1    | 2.65 | 2.70 | 2.75 | V    |

| I <sub>OUT3</sub> | Output Current           |            |      | 2    | 5    | mA   |

| V <sub>DROP</sub> | Dropout Voltage          |            |      |      | 50   | mV   |

| I <sub>QC</sub>   | Quiescent Current        |            | 4.8  | 6.6  | 9.7  | μA   |

| PSRR              | Ripple Rejection         |            |      | 40   |      | dB   |

| T <sub>R</sub>    | Rise Time                |            | 110  |      | 320  | μs   |

## **Buffered Voltage Reference**

| Symbol            | Parameter         | Conditions | Min  | Тур  | Max  | Unit |

|-------------------|-------------------|------------|------|------|------|------|

| $V_{REF}$         | Output Voltage    |            | 1.45 | 1.50 | 1.55 | V    |

| I <sub>REF</sub>  | Output Current    |            |      |      | 0.5  | mA   |

| V <sub>DROP</sub> | Dropout Voltage   |            |      |      | 50   | mV   |

| I <sub>QC</sub>   | Quiescent Current |            | 4.8  | 6.6  | 9.7  | μA   |

| I <sub>SD</sub>   | Shutdown Current  |            |      | 0.1  | 1    | μA   |

| PSRR              | Ripple Rejection  |            |      | 40   |      | dB   |

| T <sub>R</sub>    | Rise time         |            | 110  |      | 320  | μs   |

# LDO4, LDO5, LDO6

| Symbol             | Parameter                         | Conditions                                               | Min  | Тур | Max  | Unit              |

|--------------------|-----------------------------------|----------------------------------------------------------|------|-----|------|-------------------|

| V <sub>INC</sub>   | Operating Supply Voltage          |                                                          | 3    |     | 5.5  | V                 |

| V <sub>INT</sub>   | Operating Internal Supply Voltage |                                                          | 2.4  | 2.5 | 2.6  | V                 |

| V <sub>OUT</sub>   | Output Voltage                    |                                                          | 2.74 | 2.8 | 2.86 | V                 |

| I <sub>OUT</sub>   | Output Current                    |                                                          |      | 80  | 130  | mA                |

| I <sub>QC</sub>    | Quiescent Current                 |                                                          |      | 195 | 236  | μA                |

| DV <sub>OUT</sub>  | Line Regulation                   | V <sub>BAT</sub> : 3V to 3.4V, I <sub>OUT</sub> = 130 mA |      | 3   | 2    | mV                |

| DV <sub>PEAK</sub> | Line Regulation Transient         | Same as above, $T_R = T_F = 5 \ \mu s$                   |      | 4   | 2.85 | mV                |

| DVOUT              | Load Regulation                   | 10% - 90% I <sub>OUT</sub> , V <sub>BAT</sub> = 3V       |      | 10  | 1    | mV                |

|                    |                                   | 10% - 90% I <sub>OUT</sub> , V <sub>BAT</sub> = 5.0V     |      | 15  | 1    | mV                |

|                    |                                   | 10% - 90% I <sub>OUT</sub> , V <sub>BAT</sub> = 5.5V     |      | 15  | 1    | mV                |

| DV <sub>PEAK</sub> | Load Regulation Transient         | Same as above, T <sub>R</sub> = T <sub>F</sub> = 5 µs    |      | 1.2 | 2.4  | mV                |

| PSRR               | Ripple Rejection                  | F=217Hz – V <sub>BAT</sub> = 3.6V                        | 70   | 73  |      | dB                |

| V <sub>N</sub>     | Output Noise                      | BW: 10 Hz to 100 kHz                                     |      | 29  | 37   | μV <sub>RMS</sub> |

| T <sub>R</sub>     | Rise Time                         | 100% I <sub>OUT</sub> , 10% - 90% V <sub>OUT</sub>       |      |     | 50   | μs                |

| I <sub>SD</sub>    | Shut Down Current                 |                                                          |      |     | 1    | μA                |

## **Open Drain Switch**

| Table 10. | Open Drain | Switch Electrical | Characteristics |

|-----------|------------|-------------------|-----------------|

|-----------|------------|-------------------|-----------------|

| Symbol           | Parameter          | Conditions               | Min | Тур | Max | Unit |

|------------------|--------------------|--------------------------|-----|-----|-----|------|

| V <sub>OL</sub>  | Low Output Voltage | I <sub>OL</sub> = 100 mA |     |     | 0.4 | V    |

| I <sub>OL</sub>  | Low Output Current |                          |     |     | 100 | mA   |

| T <sub>ON</sub>  | Turn-on Time       |                          |     |     | 10  | μs   |

| T <sub>OFF</sub> | Turn-off Time      |                          |     |     | 10  | μs   |

Conditions are V<sub>INE</sub> = 1.8V or 2.8V,  $t_A$  = -40°C to +85°C, C<sub>DVCC</sub> = 100 nF, CSIM-V<sub>CC</sub> = 100 nF

| Symbol            | Parameter                | Conditions                                      | Min  | Тур | Max  | Unit |

|-------------------|--------------------------|-------------------------------------------------|------|-----|------|------|

| V <sub>INE</sub>  | Operating Supply Voltage | V <sub>OUT0</sub> or V <sub>OUT1</sub>          | 1.65 |     |      |      |

| V <sub>OUT7</sub> | Output Voltage           | I <sub>OUT7</sub> < 10 mA<br>EN7 = 1<br>DVB = 1 | 1.71 | 1.8 | 1.89 | V    |

| V <sub>OUT7</sub> | Output Voltage           | I <sub>OUT7</sub> < 10mA<br>EN7 = 1<br>DVB = 0  | 2.74 | 2.8 | 2.86 | V    |

| I <sub>SD</sub>   | Total Shutdown Current   | EN7 = 0                                         |      | 0.1 | 1    | μA   |

| I <sub>QC</sub>   | Quiescent Current        | Low-power Mode                                  |      | 8   | 9.5  | μA   |

| I <sub>QC</sub>   | Quiescent Current        | Full-power Mode                                 |      |     | 60   | μA   |

| I <sub>OUT7</sub> | Output Current           |                                                 |      | 10  |      | mA   |

| I <sub>SC</sub>   | Short Circuit Current    |                                                 |      |     | 40   | mA   |

### Table 11. LDO7 Electrical Characteristics.

# **Packaging Information**

Figure 10. Mechanical Package Drawing for 49-ball Ball Grid Array

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

© Atmel Corporation 2003. All rights reserved. Atmel<sup>®</sup> and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries. Bluetooth<sup>®</sup> is a registered trademark owned by the Bluetooth SIG, Inc. Other terms and product names may be the trademarks of others.

6014A-PMGMT-10/03