### **General Description**

The MAX7036 low-cost receiver is designed to receive amplitude-shift-keyed (ASK) and on-off-keyed (OOK) data in the 300MHz to 450MHz frequency range. The receiver has an RF input signal range of -109dBm to 0dBm.

The MAX7036 requires few external components and has a power-down pin to put it in a low-current sleep mode, making it ideal for cost- and power-sensitive applications. The low-noise amplifier (LNA), phaselocked loop (PLL), mixer, IF filter, received-signalstrength indicator (RSSI), and baseband sections are all on-chip. The MAX7036 uses a very-low intermediate frequency (VLIF) architecture. The MAX7036 integrates the IF filter on-chip and therefore eliminates an external ceramic filter, reducing the bill-of-materials cost. The device also contains an on-chip automatic gain control (AGC) that reduces the LNA gain by 30dB when the input signal power is large. The MAX7036 operates from either a 5V or a 3.3V power supply and draws 5.5mA (typ) of current.

The MAX7036 is available in a 20-pin thin QFN package with an exposed pad and is specified over the AEC-Q100 Level 2 (-40°C to +105°C) temperature range.

### **Applications**

Low-Cost RKE Garage Door Openers Remote Controls Home Automation Sensor Networks Security Systems

## Features

- ♦ ASK/OOK Modulation

- ♦ < 250µs Enable Turn-On Time

- ♦ On-Chip PLL, VCO, Mixer, IF, Baseband

- ♦ Low IF (200kHz Nominal)

- ♦ 5.5mA DC Current

- ♦ 1µA Standby Current

- ♦ 3.3V/5V Operation

- ♦ Small 20-Pin Thin QFN Package with an Exposed

### **Ordering Information**

| PART          | TEMP RANGE      | PIN-PACKAGE     |  |  |

|---------------|-----------------|-----------------|--|--|

| MAX7036GTP/V+ | -40°C to +105°C | 20 Thin QFN-EP* |  |  |

N denotes an automotive qualified part.

- +Denotes a lead(Pb)-free/RoHS-compliant package.

- \*EP = Exposed pad.

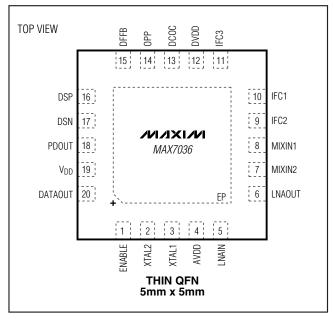

## Pin Configuration

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND0.3V to +6.0V                     | Ju |

|---------------------------------------------------------|----|

| AVDD to GND0.3V to +4.0V                                |    |

| DVDD to GND0.3V to +4.0V                                | Ju |

| ENABLE to GND0.3V to (V <sub>DD</sub> + 0.3V)           |    |

| LNAIN to GND0.3V to +1.2V                               | 0  |

| All Other Pins to GND0.3V to (V <sub>DVDD</sub> + 0.3V) | Ju |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)   | St |

| 20-Pin TQFN (derate 20.8mW/°C above +70°C)1666.7mW      | Le |

|                                                         |    |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) (Note 1)<br>20-Pin TQFN2°C<br>Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) (Note 1) | )/W |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 20-Pin TQFN48°C                                                                                                                                         | )/W |

| Operating Temperature Range40°C to +105                                                                                                                 | 5°C |

| Junction Temperature+150                                                                                                                                | )°C |

| Storage Temperature Range65°C to +150                                                                                                                   |     |

| Lead Temperature (soldering, 10s)+300                                                                                                                   | )°C |

| Soldering Temperature (reflow)+260                                                                                                                      |     |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a single-layer board. For detailed information on package thermal considerations, go to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 3.3V DC ELECTRICAL CHARACTERISTICS

(*Typical Application Circuit*,  $50\Omega$  system impedance,  $V_{AVDD} = V_{DVDD} = V_{DD} = 3.0V$  to 3.6V,  $f_{RF} = 300MHz$  to 450MHz,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = V_{DD} = 3.3V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (100% tested at  $T_A = +105^{\circ}C$ .)

| PARAMETER                | SYMBOL          | CON                                                                 | IDITIONS                         | MIN                   | TYP | MAX | UNITS |

|--------------------------|-----------------|---------------------------------------------------------------------|----------------------------------|-----------------------|-----|-----|-------|

| Supply Voltage           | $V_{DD}$        | V <sub>A</sub> V <sub>DD</sub> = V <sub>D</sub> V <sub>DD</sub> = V | /DD                              | 3.0                   | 3.3 | 3.6 | V     |

|                          |                 |                                                                     | $f_{RF} = 315MHz$                |                       | 5.3 | 6.7 | νο Λ  |

| Cumply Current           | I.e.            | T 105°C                                                             | $f_{RF} = 433MHz$                |                       | 5.8 | 7.3 | mA    |

| Supply Current           | IIN             | T <sub>A</sub> < +105°C                                             | Deep-sleep mode,<br>VENABLE = 0V |                       | 1   | 2.7 | μА    |

| DIGITAL INPUT (ENABLE)   |                 | ·                                                                   |                                  |                       |     |     |       |

| Input High Voltage       | VIH             | V <sub>AVDD</sub> = V <sub>DVDD</sub> = V <sub>DD</sub>             |                                  | V <sub>DD</sub> - 0.4 |     |     | V     |

| Input Low Voltage        | V <sub>IL</sub> | $V_{AVDD} = V_{DVDD} = V_{DD}$                                      |                                  |                       |     | 0.4 | V     |

| Input Current            | IENABLE         | 0 ≤ V <sub>ENABLE</sub> ≤ V <sub>DD</sub>                           |                                  |                       |     | 20  | μΑ    |

| DIGITAL OUTPUT (DATAOUT) |                 |                                                                     |                                  |                       |     |     |       |

| Output Low Voltage       | V <sub>OL</sub> | I <sub>SINK</sub> = 100µA                                           |                                  |                       |     | 0.4 | V     |

| Output High Voltage      | VoH             | ISOURCE = 100µA                                                     |                                  | V <sub>DD</sub> - 0.4 |     |     | V     |

### 5.0V DC ELECTRICAL CHARACTERISTICS

(Typical Application Circuit,  $50\Omega$  system impedance,  $V_{DD} = 4.5V$  to 5.5V,  $f_{RF} = 300MHz$  to 450MHz,  $T_A = -40^{\circ}C$  to +105°C, unless otherwise noted. Typical values are at  $V_{DD} = 5.0V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (100% tested at  $T_A = +105^{\circ}C$ .)

| PARAMETER                | SYMBOL   | CONI                                                            | DITIONS                          | MIN                   | TYP | MAX | UNITS |

|--------------------------|----------|-----------------------------------------------------------------|----------------------------------|-----------------------|-----|-----|-------|

| Supply Voltage           | $V_{DD}$ |                                                                 |                                  | 4.5                   | 5.0 | 5.5 | V     |

|                          |          |                                                                 | f <sub>RF</sub> = 315MHz         |                       | 5.4 | 6.8 | т Л   |

| Cupply Current           | lu.      | Ta < +105°C                                                     | $f_{RF} = 433MHz$                |                       | 5.9 | 7.4 | mA    |

| Supply Current           | IIN      | 1A < +105 C                                                     | Deep-sleep mode,<br>VENABLE = 0V |                       | 1   | 3.4 | μΑ    |

| DIGITAL INPUT (ENABLE)   |          |                                                                 |                                  |                       |     |     |       |

| Input High Voltage       | VIH      | V <sub>A</sub> V <sub>DD</sub> = V <sub>D</sub> V <sub>DD</sub> |                                  | V <sub>DD</sub> - 0.4 |     |     | V     |

| Input Low Voltage        | VIL      | V <sub>A</sub> V <sub>DD</sub> = V <sub>D</sub> V <sub>DD</sub> |                                  |                       |     | 0.4 | V     |

| Input Current            | IENABLE  | 0 ≤ V <sub>ENABLE</sub> ≤ V <sub>DD</sub>                       |                                  |                       |     | 20  | μΑ    |

| DIGITAL OUTPUT (DATAOUT) |          |                                                                 |                                  |                       |     |     |       |

| Output Low Voltage       | VoL      | I <sub>SINK</sub> = 100µA                                       |                                  |                       |     | 0.4 | V     |

| Output High Voltage      | Voн      | ISOURCE = 100µA                                                 |                                  | V <sub>DD</sub> - 0.4 |     |     | V     |

### **AC ELECTRICAL CHARACTERISTICS**

$(Typical\ Application\ Circuit,\ 50\Omega\ system\ impedance,\ VAVDD = VDVDD = VDD = 3.0V\ to\ 3.6V,\ fRF = 300MHz\ to\ 450MHz,\ TA = -40°C\ to\ +105°C,\ unless\ otherwise\ noted.\ Typical\ values\ are\ at\ VAVDD = VDVDD = VDD = 3.3V,\ TA = +25°C,\ fRF = 315MHz,\ unless\ otherwise\ noted.\ (100%\ tested\ at\ TA = +105°C.)$

| PARAMETER                                   | SYMBOL                    | CONE                                 | DITIONS                                  | MIN | TYP  | MAX | UNITS |

|---------------------------------------------|---------------------------|--------------------------------------|------------------------------------------|-----|------|-----|-------|

| Receiver Input Frequency Range              | fRF                       |                                      |                                          | 300 |      | 450 | MHz   |

| Maximum Receiver Input Level                | PRFIN                     |                                      |                                          |     | 0    |     | dBm   |

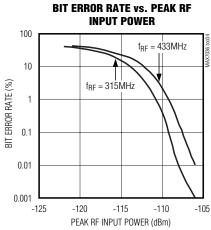

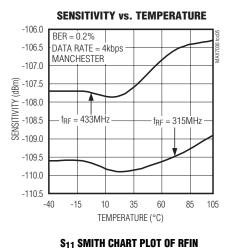

| Sensitivity (Note 2)                        |                           | f <sub>RF</sub> = 315MHz             |                                          |     | -109 |     | dBm   |

| Sensitivity (Note 2)                        |                           | f <sub>RF</sub> = 433MHz             |                                          |     | -107 |     | abin  |

| Power-On Time                               | toN output, do include ba | Time for valid RSSI output, does not | Enable power on (V <sub>DD</sub> > 3.0V) |     | 250  |     | μs    |

| Fower-Off Time                              |                           | include baseband filter settling     | V <sub>DD</sub> power on                 |     | 1    |     | ms    |

| AGC Hysteresis                              |                           |                                      |                                          |     | 5    |     | dB    |

| AGC Low Gain-to-High Gain<br>Switching Time |                           |                                      |                                          |     | 13   |     | ms    |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

(*Typical Application Circuit*,  $50\Omega$  system impedance,  $V_{AVDD} = V_{DDD} = V_{DD} = 3.0V$  to 3.6V,  $f_{RF} = 300MHz$  to 450MHz,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{AVDD} = V_{DVDD} = V_{DD} = 3.3V$ ,  $T_A = +25^{\circ}C$ ,  $f_{RF} = 315MHz$ , unless otherwise noted.) (100% tested at  $T_A = +105^{\circ}C$ .)

| PARAMETER                          | SYMBOL             | COND                                                                     | DITIONS                  | MIN  | TYP           | MAX   | UNITS |  |

|------------------------------------|--------------------|--------------------------------------------------------------------------|--------------------------|------|---------------|-------|-------|--|

| LNA/MIXER                          |                    |                                                                          |                          |      |               |       |       |  |

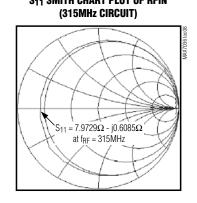

| LNA lpput lmpedance                | 7                  | Normalized to $50\Omega$                                                 | f <sub>RF</sub> = 315MHz |      | 0.4 -<br>j5.6 |       | Ω     |  |

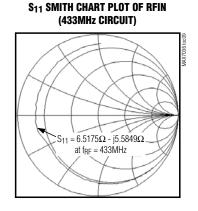

| LNA Input Impedance                | Z <sub>INLNA</sub> | Normalized to 5012                                                       | f <sub>RF</sub> = 433MHz |      | 0.4 -<br>j4.0 |       | 52    |  |

| LO Signal Feedthrough to Antenna   |                    |                                                                          |                          |      | -75           |       | dBm   |  |

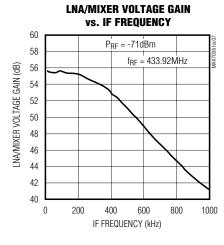

| Voltage Gain Reduction             |                    | Low-gain mode, AGC                                                       | enabled                  |      | 29            |       | dB    |  |

| LNIA/Miyor Voltage Coip            |                    | High-gain LNA mode                                                       |                          |      | 55            |       | ٩D    |  |

| LNA/Mixer Voltage Gain             |                    | Low-gain LNA mode                                                        |                          |      | 26            |       | dB    |  |

| 3dB Cutoff Frequency               | BWIF               | Set by capacitors on IFC1 and IFC2 (see the Typical Application Circuit) |                          |      | 400           |       | kHz   |  |

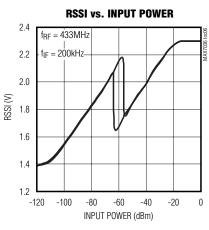

| RSSI Linearity                     |                    |                                                                          |                          |      | ±0.5          |       | dB    |  |

| RSSI Dynamic Range                 |                    | Includes AGC                                                             |                          |      | 80            |       | dB    |  |

| RSSI Level                         |                    | P <sub>RFIN</sub> < -120dBm                                              |                          |      | 1.34          |       | V     |  |

| HSSI Level                         |                    | PRFIN > 0dBm, AGC                                                        | enabled                  | 2.35 |               | V     |       |  |

| Intermediate Frequency             | fIF                |                                                                          |                          |      | 200           |       | kHz   |  |

| Maximum Data-Filter Bandwidth      | BW <sub>DF</sub>   |                                                                          |                          |      | 50            |       | kHz   |  |

| Maximum Data-Slicer Bandwidth      | BW <sub>DS</sub>   |                                                                          |                          |      | 100           |       | kHz   |  |

| Maximum Peak Detector<br>Bandwidth |                    |                                                                          |                          |      | 50            |       | kHz   |  |

| Maximum Data Rate                  |                    | Manchester coded                                                         |                          |      | 33            |       | khns  |  |

| I Maximum Dala Hale                |                    | Nonreturn to zero (NF                                                    | RZ)                      | 66   |               |       | kbps  |  |

| Crystal Frequency                  | fxtal              |                                                                          |                          |      |               | 14.06 | MHz   |  |

| Crystal Load Capacitance           | CLOAD              |                                                                          |                          |      | 10            |       | рF    |  |

**Note 2:** BER =  $2 \times 10^{-3}$ , Manchester coded, data rate = 4kbps. IF bandwidth = 400kHz.

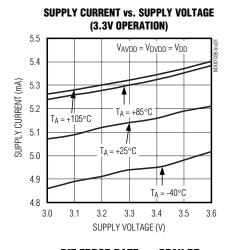

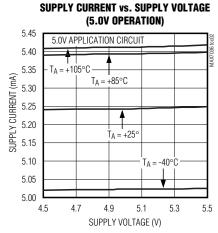

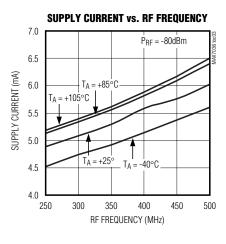

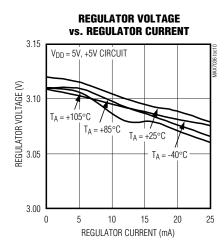

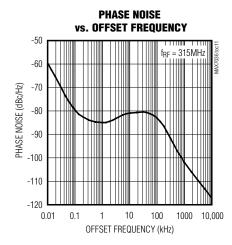

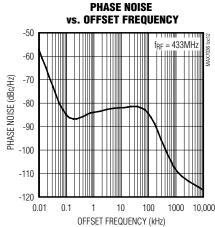

### Typical Operating Characteristics

(Typical Application Circuit, VAVDD = VDD = VDVDD = 3.3V, fRF = 315MHz, TA = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(*Typical Application Circuit*, V<sub>AVDD</sub> = V<sub>DD</sub> = V<sub>DVDD</sub> = 3.3V, f<sub>RF</sub> = 315MHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

## **Pin Description**

| PIN               | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                         |

|-------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | ENABLE | Enable Input. Internally pulled down to ground. Set V <sub>ENABLE</sub> = V <sub>DD</sub> for normal operation.                                                                                                                                                                                                  |

| 2                 | XTAL2  | Crystal Input 2. Connect an external crystal from XTAL2 to XTAL1. Bypass to GND if XTAL1 is driven from an AC-coupled external reference (see the <i>Crystal Oscillator</i> section).                                                                                                                            |

| 3                 | XTAL1  | Crystal Input 1. Connect an external crystal from XTAL2 to XTAL1. Can also be driven with an AC-coupled external reference oscillator (see the <i>Crystal Oscillator</i> section).                                                                                                                               |

| 4                 | AVDD   | Positive Analog Supply Voltage. Connect to DVDD. Bypass to GND with a 0.1µF capacitor as close as possible to the device (see the <i>Typical Application Circuit</i> ). For 5.0V operation, AVDD is internally connected to an on-chip 3.2V LDO regulator. For 3.3V operation, connect AVDD to V <sub>DD</sub> . |

| 5                 | LNAIN  | Low-Noise Amplifier Input. Must be AC-coupled (see the Low-Noise Amplifier section).                                                                                                                                                                                                                             |

| 6                 | LNAOUT | Low-Noise Amplifier Output. Must be connected to AVDD through a parallel LC tank circuit. ACcouple to MIXIN2 (see the <i>Low-Noise Amplifier</i> section).                                                                                                                                                       |

| 7                 | MIXIN2 | 2nd Differential Mixer Input. Connect to the LNAOUT side of the LC tank filter through a 100pF capacitor (see the <i>Typical Application Circuit</i> ).                                                                                                                                                          |

| 8                 | MIXIN1 | 1st Differential Mixer Input. Connect to the AVDD side of the LC tank filter through a 100pF capacitor (see the <i>Typical Application Circuit</i> ).                                                                                                                                                            |

| 9                 | IFC2   | IF Filter Capacitor Connection 2. This is for the Sallen-Key IF filter. Connect a capacitor from IFC2 to GND. The value of the capacitor is determined by the IF filter bandwidth (see the <i>Typical Application Circuit</i> ).                                                                                 |

| 1 1()   IE(;1   ' |        | IF Filter Capacitor Connection 1. This is for the Sallen-Key IF filter. Connect a capacitor from IFC1 to IFC3. The value of the capacitor is determined by the IF filter bandwidth (see the <i>Typical Application Circuit</i> ).                                                                                |

| 11                | IFC3   | IF Filter Capacitor Connection 3. This is for the Sallen-Key IF filter. Connect a capacitor from IFC3 to IFC1. The value of the capacitor is determined by the IF filter bandwidth (see the <i>Typical Application Circuit</i> ).                                                                                |

| 12                | DVDD   | Positive Digital Supply Voltage Input. Connect to AVDD. Bypass to GND with a 0.01µF capacitor as close as possible to the device (see the <i>Typical Application Circuit</i> ).                                                                                                                                  |

## Pin Description (continued)

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                              |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | DCOC            | DC Offset Capacitor Connection. This is for the RSSI amplifier. Connect a 1µF capacitor from this pin to ground (see the <i>Typical Application Circuit</i> ).                                                                                                        |

| 14  | OPP             | Noninverting Op-Amp Input. This is for the Sallen-Key data filter. Connect a capacitor from this pin to GND. The value of the capacitor is determined by the data-filter bandwidth.                                                                                   |

| 15  | DFFB            | Data-Filter Feedback Input. Input for the feedback of the Sallen-Key data filter. Connect a capacitor from this pin to DSP. The value of the capacitor is determined by the data-filter bandwidth.                                                                    |

| 16  | DSP             | Positive Data-Slicer Input. Connect a capacitor from this pin to DFFB. The value of the capacitor is determined by the data-filter bandwidth.                                                                                                                         |

| 17  | DSN             | Negative Data-Slicer Input                                                                                                                                                                                                                                            |

| 18  | PDOUT           | Peak-Detector Output                                                                                                                                                                                                                                                  |

| 19  | V <sub>DD</sub> | Power-Supply Voltage Input. For 5.0V operation, V <sub>DD</sub> is the input to an on-chip voltage regulator whose 3.2V output drives AVDD. Bypass to ground with a 0.1µF capacitor as close as possible to the device (see the <i>Typical Application Circuit</i> ). |

| 20  | DATAOUT         | Digital Baseband Data Output                                                                                                                                                                                                                                          |

| _   | EP              | Exposed Pad. Internally connected to ground. Connect to a large ground plane using multiple vias to maximize thermal and electrical performance.                                                                                                                      |

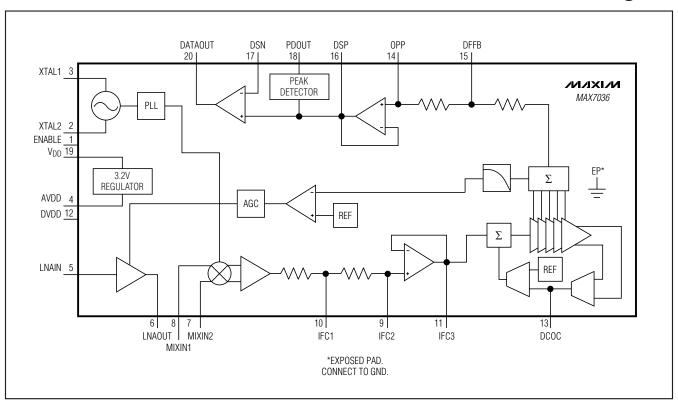

## **Functional Diagram**

### \_Detailed Description

The MAX7036 CMOS RF receiver, and a few external components, provide the complete receiver chain from the antenna to the digital output data. Depending on signal power and component selection, data rates as high as 33kbps Manchester (66kbps NRZ) can be achieved.

The MAX7036 is designed to receive binary ASK/OOK data modulated in the 300MHz to 450MHz frequency range. ASK modulation uses a difference in amplitude of the carrier to represent digital data.

#### **Voltage Regulator**

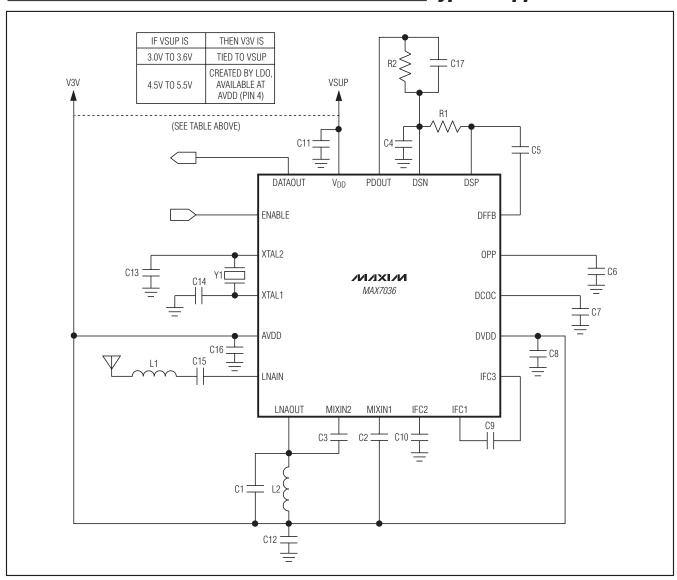

For operation with a single 3.0V to 3.6V supply voltage, connect AVDD, DVDD, and  $V_{DD}$  to the supply voltage. For operation with a single 4.5V to 5.5V supply voltage, connect  $V_{DD}$  to the supply voltage. An on-chip voltage regulator drives the AVDD pin to approximately 3.2V. For proper operation, connect DVDD and AVDD together. Bypass  $V_{DD}$  and AVDD to GND with 0.1 $\mu$ F capacitors placed as close as possible to the device. Bypass DVDD to GND with a 0.01 $\mu$ F capacitor (see the *Typical Application Circuit*).

#### **Low-Noise Amplifier**

The LNA is an nMOS cascode amplifier. The LNA and mixer have a combined 55dB voltage gain. The gain and noise figures are dependent on both the antennamatching network at the LNA input and the LC tank network between the LNA output and the mixer inputs.

L2 and C1 comprise the LC tank filter connected to LNAOUT (see the *Typical Application Circuit*). L2 also serves as a bias inductor to LNAOUT. Bypass the power-supply side of L2 to GND with a capacitor that provides a low-impedance path at the RF carrier frequency (e.g., 220pF). Select L2 and C1 to resonate at the desired RF input frequency. The resonant frequency is given by:

$$f_{RF} = \frac{1}{2\pi\sqrt{L_{TOTAL} \times C_{TOTAL}}}$$

where LTOTAL = L2 + LPARASITICS and CTOTAL = C1 + CPARASITICS.

LPARASITICS and CPARASITICS include inductance and capacitance of the PCB traces, package pins, mixer input impedance, LNA output impedance, etc. At high frequencies, these parasitics can have a dramatic effect on the tank filter center frequency and must not be ignored. The total parasitic capacitance is generally 4pF to 6pF. Adjust L2 and C1 accordingly to achieve the desired tank center frequency.

#### **Automatic Gain Control (AGC)**

The AGC circuit monitors the RSSI output. The AGC switches to its low-gain state when the RSSI output reaches 2.2V. The AGC gain reduction is typically 29dB, corresponding to an RSSI voltage drop of 435mV. The LNA resumes high-gain mode when the RSSI level drops back below 1.67V for 13ms for 315MHz and 10ms for 433MHz operation. The AGC has a hysteresis of 5dB. With this AGC function, the MAX7036 can reliably produce an ASK output for RF input levels up to 0dBm, with modulation depth of 30dB.

#### Mixer

The mixer cell is a double-balanced mixer that performs a downconversion of the RF input to a typical IF of 200kHz from either a high-side or a low-side injected LO. The mixer output drives the input of the on-chip IF filter.

#### Phase-Locked Loop (PLL)

The PLL block contains a phase detector, charge pump, integrated loop filter, VCO, asynchronous clock dividers, and crystal-oscillator driver. Besides the crystal, this PLL does not require any external components. The VCO generates the LO. The relationship between the RF, IF, and crystal reference frequencies is given by:

$$f_{XTAL} = \frac{f_{LO}}{32}$$

where  $f_{LO} = f_{RF} \pm f_{IF}$

#### Received-Signal-Strength Indicator (RSSI)

The RSSI circuit provides a DC output proportional to the logarithm of the input power level. RSSI output voltage has a slope of about 14.5mV/dB (of input power). The RSSI monotonic dynamic range exceeds 80dB. This includes the 30dB of AGC.

## Applications Information

#### **Crystal Oscillator**

The crystal (XTAL) oscillator in the MAX7036 is designed to present a capacitance of approximately 4pF between XTAL1 and XTAL2. In most cases, this corresponds to a 6pF load capacitance applied to the external crystal when typical PCB parasitics are added. The MAX7036 is designed to operate with a typical 10pF load capacitance crystal. It is very important to use a crystal with a load capacitance equal to the capacitance of the MAX7036 crystal oscillator plus PCB parasitics. If a crystal designed to oscillate with a different load capacitance is used, the crystal is pulled away from its stated operating frequency, introducing

an error in the reference frequency. A crystal designed to operate at a higher load capacitance than the value specified for the oscillator is always pulled higher in frequency. Adding capacitance to increase the load capacitance on the crystal increases the start-up time and may prevent oscillation altogether.

In actuality, the oscillator pulls every crystal. The crystal's natural frequency is really below its specified frequency, but when loaded with the specified load capacitance, the crystal is pulled and oscillates at its specified frequency. This pulling is already accounted for in the specification of the load capacitance.

Additional pulling can be calculated if the electrical parameters of the crystal are known. The frequency pulling is given by:

$$f_{p} = \frac{C_{M}}{2} \left( \frac{1}{C_{CASE} + C_{LOAD}} - \frac{1}{C_{CASE} + C_{SPEC}} \right) \times 10^{6}$$

where

$\ensuremath{f_{\text{p}}}$  is the amount the crystal frequency is pulled in ppm.

C<sub>M</sub> is the motional capacitance of the crystal.

CCASE is the case capacitance.

CSPEC is the specified load capacitance.

CLOAD is the actual load capacitance.

When the crystal is loaded, as specified (i.e., C<sub>LOAD</sub> = C<sub>SPFC</sub>), the frequency pulling equals zero.

It is possible to use an external reference oscillator in place of a crystal to drive the VCO. AC-couple the external oscillator to XTAL1 with a 1000pF capacitor. Drive XTAL1 with a signal level of approximately -10dBm. AC-couple XTAL2 to ground with a 1000pF capacitor.

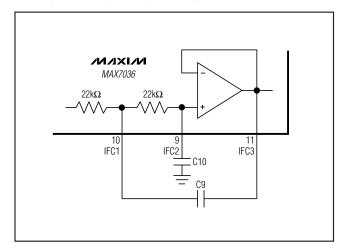

#### **IF Filter**

The IF filter is a 2nd-order Butterworth lowpass filter preceded by a low-frequency DC block. The lowpass filter is implemented as a Sallen-Key filter using an internal op amp and two on-chip  $22k\Omega$  resistors. The pole locations are set by the combination of the on-chip resistors and two external capacitors (C9 and C10, Figure 1). The values of these two capacitors for a 3dB cutoff frequency of 400kHz are given below:

$$\begin{split} C9 &= \frac{1}{\big(1.414\big)(R)\big(f_{C}\big)} = \frac{1}{\big(1.414\big)\big(22k\Omega\big)\big(3.14\big)\big(400kHz\big)} = 26pF \\ C10 &= \frac{1}{\big(2.828\big)(R)\big(\pi\big)\big(f_{C}\big)} = \frac{1}{\big(2.828\big)\big(22k\Omega\big)\big(3.14\big)\big(400kHz\big)} = 13pF \end{split}$$

Because the stray shunt capacitance at each of the pins (IFC1 and IFC2) on a typical PCB is approximately 2pF, choose the value of the external capacitors to be approximately 2pF lower than the desired total capacitance. Therefore, the practical values for C9 and C10 are 22pF and 10pF, respectively.

Figure 1. Sallen-Key Lowpass IF Filter

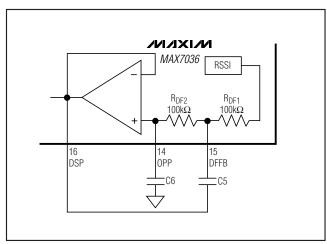

#### **Data Filter**

The data filter is implemented as a 2nd-order lowpass Sallen-Key filter. The pole locations are set by the combination of two on-chip resistors and two external capacitors. Adjusting the value of the external capacitors changes the corner frequency to optimize for different data rates. Set the corner frequency to approximately 1.5 times the fastest Manchester expected data rate from the transmitter. Keeping the corner frequency near the data rate rejects any noise at higher frequencies, resulting in an increase in receiver sensitivity.

The configuration shown in Figure 2 can create a Butterworth or Bessel response. The Butterworth filter offers a very flat amplitude response in the passband and a rolloff rate of 40dB/decade for the two-pole filter. The Bessel filter has a linear phase response, which works with the coefficients in Table 1.

$$C5 = \frac{b}{a(100k)(\pi)(f_C)}$$

$$C6 = \frac{a}{4(100k)(\pi)(f_C)}$$

where fC is the desired corner frequency.

For example, to choose a Butterworth filter response with a corner frequency of 6kHz:

$$C5 = \frac{1.000}{(1.414)(100k\Omega)(3.14)(6kHz)} = 375pF$$

$$C6 = \frac{1.414}{(4)(100k\Omega)(3.14)(6kHz)} = 186pF$$

Choosing standard capacitor values changes C5 to 390pF and C6 to 180pF, as shown in the *Typical Application Circuit*.

Table 1. Coefficients to Calculate C5 and C6

| FILTER TYPE             | а      | b     |

|-------------------------|--------|-------|

| Butterworth (Q = 0.707) | 1.414  | 1.000 |

| Bessel (Q = 0.577)      | 1.3617 | 0.618 |

Figure 2. Sallen-Key Lowpass Data Filter

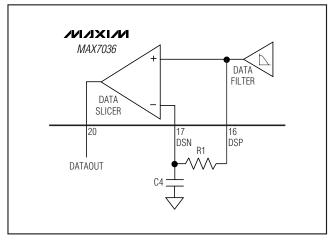

#### **Data Slicer**

The data slicer takes the analog output of the data filter and converts it to a digital signal. This is achieved by using a comparator and comparing the analog input to a threshold voltage. One input is supplied by the data-filter output. Both comparator inputs are accessible off chip to allow for different methods of generating the slicing threshold, which is applied to the second comparator input.

The suggested data-slicer configuration uses a resistor (R1) connected between DSN and DSP with a capacitor (C4) from DSN to GND (Figure 3). This configuration averages the analog output of the filter and sets the threshold to approximately 50% of that amplitude. With this configuration, the threshold automatically adjusts as the analog signal varies, minimizing the possibility for errors in the digital data. The values of R1 and C4 affect how fast the threshold tracks to the analog amplitude. Be sure to keep the corner frequency of the RC circuit much lower than the lowest expected data rate.

Figure 3. Generating Data-Slicer Threshold

Note that a long string of zeros or ones can cause the threshold to drift. This configuration works best if a coding scheme (e.g., Manchester coding, which has an equal number of zeros and ones) is used.

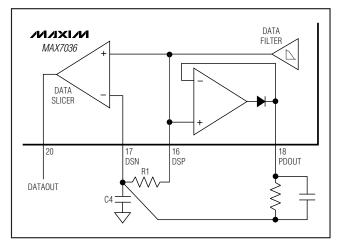

#### **Peak Detector**

The peak-detector output (PDOUT), in conjunction with an external RC filter, creates a DC output voltage equal to the peak value of the data signal. The resistor provides a path for the capacitor to discharge, allowing the peak detector to dynamically follow peak changes of the data-filter output voltage. The peak detector can be used for at least two functions. First, it can serve as an RSSI for ASK modulation. Second, it can be used for faster data-slicer response by adding it to the threshold pin (DSN) on the data-slicer comparator (Figure 4). The two capacitors in this circuit should be equal, and the peak detector resistor should be approximately 10

times larger than the resistor in the RC smoothing circuit between DSP and DSN. This circuit will provide an instantaneous jump of one-half of the DSP increase from "no signal" voltage to peak voltage, which then decays with the same time constant as that of the threshold build-up from the RC smoothing circuit. The DC slicing voltage at DSN is slightly higher (by the ratio of the two resistors in the circuit) than it would be without the speed-up circuit. Always provide a capacitive path from the PDOUT pin to ground when using the peak-detector output.

Figure 4. Using PDOUT for Faster Startup

#### **Layout Considerations**

A properly designed PCB is an essential part of any RF/microwave circuit. On high-frequency inputs and outputs, use controlled-impedance lines and keep them as short as possible to minimize losses and radiation. At high frequencies, trace lengths that are  $\lambda/10$  or longer act as antennas.

Keeping the traces short also reduces parasitic inductance. Generally, 1in of a PCB trace adds about 20nH of parasitic inductance. The parasitic inductance can have a dramatic effect on the effective inductance of a passive component. For example, a 0.5in trace connecting a 100nH inductor adds an extra 10nH of inductance or 10%.

To reduce the parasitic inductance, use wider traces and a solid ground or power plane below the signal traces. Also, use low-inductance connections to ground on all GND pins, and place decoupling capacitors close to all power-supply connections.

**Table 2. Component Values**

| COMPONENT | f <sub>RF</sub> = 315MHz | f <sub>RF</sub> = 433.92MHz |

|-----------|--------------------------|-----------------------------|

| C1        | 4.7pF                    | 2.7pF                       |

| C2        | 100pF                    | 100pF                       |

| C3        | 100pF                    | 100pF                       |

| C4        | 0.1µF                    | 0.1µF                       |

| C5        | 390pF                    | 390pF                       |

| C6        | 180pF                    | 180pF                       |

| C7        | 1µF                      | 1µF                         |

| C8        | 0.01µF                   | 0.01µF                      |

| C9        | 22pF                     | 22pF                        |

| C10       | 10pF                     | 10pF                        |

| C11       | 0.1µF                    | 0.1µF                       |

| C12       | 220pF                    | 220pF                       |

| C13       | 10pF                     | 10pF                        |

| C14       | 10pF                     | 10pF                        |

| C15       | 100pF                    | 100pF                       |

| C16       | 0.1µF                    | 0.1µF                       |

| L1        | 100nH                    | 47nH                        |

| L2        | 27nH                     | 15nH                        |

| R1        | 22kΩ                     | 22kΩ                        |

| Y1        | 9.8375MHz                | 13.55375MHz                 |

### **Typical Application Circuit**

### **Chip Information**

PROCESS: CMOS

### Package Information

For the latest package outline information and land patterns, go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|-------------|---------------------|

| 20 Thin QFN-EP  |                 | 21-0140     | 90-0008             |

\_\_\_\_\_\_/N/1XI/N

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                     | PAGES<br>CHANGED  |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 0                  | 3/09             | Initial release                                                                                                                                                 | _                 |

| 1                  |                  | Updated Absolute Maximum Ratings, TOCs 5, 11, and 12, Pin Description, Phase-Locked Loop (PLL) and Crystal Oscillator sections, and Typical Application Circuit | 2, 5, 6, 8, 9, 12 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.