# 3.3V/2.5V PHASE-LOCK LOOP CLOCK DRIVER ZERO DELAY BUFFER

### PRODUCT DISCONTINUATION NOTICE - LAST TIME BUY EXPIRES OCT 28, 2014

### FEATURES:

- Phase-lock loop clock distribution for high performance clock tree applications

- Output enable bank control

- External feedback (FBIN) pin is used to synchronize the outputs to the clock input signal

- · No external RC network required for PLL loop stability

- Operates at 3.3V/2.5V Vcc

- · Spread Spectrum Compatible

- Operating frequency up to 200MHz

- Compatible with Motorola MPC9352

- · Available in 32-pin TQFP package

- Use replacement part: 87952AYILF

### DESCRIPTION:

The 5V9352 is a low-skew, low-jitter, phase-lock loop (PLL) clock driver targeted for high performance clock tree applications. It uses a PLL to precisely align, in both frequency and phase. The 5V9352 operates at 2.5V and 3.3V.

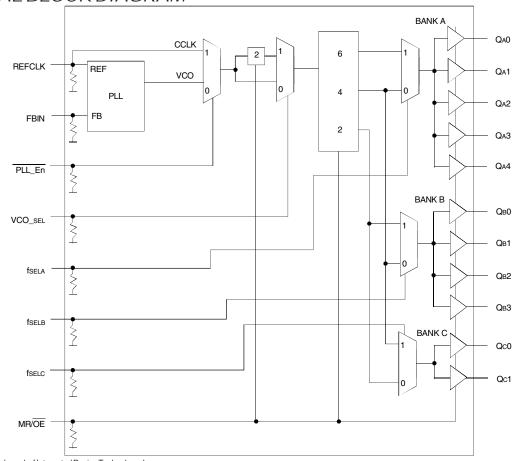

### FUNCTIONAL BLOCK DIAGRAM

The 5V9352 features three banks of individually configurable outputs. The banks are configured with five, four, and two outputs. The internal divide circuitry allows for output frequency ratios of 1:1, 2:1, 3:1, and 3:2:1. The output frequency relationship is controlled by the fSEL frequency control pins. The fSEL pins, as well as other inputs, are LVCMOS/LVTTL compatible inputs

Unlike many products containing PLLs, the 5V9352 does not require external RC networks. The loop filter for the PLL is included on-chip, minimizing component count, board space, and cost.

Because it is based on PLL circuitry, the 5V9352 requires a stabilization time to achieve phase lock of the feedback signal to the reference signal. This stabilization time is required, following power up and application of a fixed-frequency, fixed-phase signal at REFCLK, as well as following any changes to the PLL reference or feedback signals. The PLL can be bypassed for test purposes by setting the  $\overline{\text{PLL}_{EN}}$  to high.

The 5V9352 is available in Industrial temperature range (-40°C to +85°C).

1

The IDT logo is a registered trademark of Integrated Device Technology, Inc. INDUSTRIAL TEMPERATURE RANGE

## PINCONFIGURATION

**TOP VIEW**

ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol | Symbol Rating             |                 | Unit |

|--------|---------------------------|-----------------|------|

| Vcc    | Supply Voltage Range      | -0.3 to +3.6    | V    |

| Vi     | Input Voltage Range       | -0.3 to VCC+0.3 | V    |

| lin    | Input Current             | ±20             | mA   |

| Ιουτ   | DC Output Current         | ±50             | mA   |

| Tstg   | Storage Temperature Range | -65 to +125     | °C   |

NOTE:

1. Stresses beyond those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. These are stress rating only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability.

## GENERAL SPECIFICATIONS

| Symbol | Description                       | Min. | Тур.  | Max. | Unit |

|--------|-----------------------------------|------|-------|------|------|

| Vtt    | Output Termination Voltage        |      | Vcc/2 |      | V    |

| HBM    | ESD Protection (human body model) | 2000 |       |      | V    |

| LU     | Latch-Up Immunity                 | 200  |       |      | mA   |

#### CAPACITANCE

| Parameter | Description                      | Min. | Тур. | Max. | Unit |

|-----------|----------------------------------|------|------|------|------|

| Cin       | Input Capacitance                | _    | 4    | _    | pF   |

| Cpd       | Power Dissipation<br>Capacitance | _    | 10   |      | pF   |

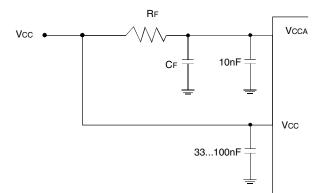

## LOGIC DIAGRAM<sup>(1,2)</sup>

#### NOTES:

- 1. IDT5V9352 requires an external RC filter for the analog power supply pin Vcca.

- 2. For Vcc = 2.5V, RF = 9-10 $\Omega$ , CF = 22 $\mu$ F.

- For Vcc = 3.3V, RF =  $5-15\Omega$ , CF =  $22\mu$ F.

#### IDT5V9352 3.3V/2.5V PHASE-LOCK LOOP CLOCK DRIVER ZERO DELAY BUFFER

#### **INDUSTRIAL TEMPERATURE RANGE**

### FUNCTION TABLES

| fsela | Qan | <b>f</b> SELB | QBN | <b>f</b> SELC | Qcn |

|-------|-----|---------------|-----|---------------|-----|

| 0     | ÷4  | 0             | ÷4  | 0             | ÷2  |

| 1     | ÷6  | 1             | ÷2  | 1             | ÷4  |

| Control Pin | Logic 0       | Logic 1                                                         |

|-------------|---------------|-----------------------------------------------------------------|

| VCO_SEL     | fVCO          | fVCO / 2                                                        |

| MR/OE       | Output Enable | Outputs disable (high-impedance state) and reset of the device. |

| PLL_En      | Enable PLL    | Disable PLL                                                     |

NOTE:

1. IDT5V9352 requires reset at power up and after any loss of PLL lock. Length of reset pulse should be greater than two REF CLK cycles (REFCLK).

### PINDESCRIPTION

| Tern      | ninal           |        |                                                                                                                |

|-----------|-----------------|--------|----------------------------------------------------------------------------------------------------------------|

| Name      | No.             | Туре   | Description                                                                                                    |

| REFCLK    | 6               | I      | Reference clock input                                                                                          |

| FBIN      | 8               | I      | Feedback input.                                                                                                |

| VCCA      | 10              | PWR    | Analog power supply                                                                                            |

| GND       | 7, 13, 17, 24,  | Ground | Negative power supply                                                                                          |

|           | 28, 29          |        |                                                                                                                |

| VCO_SEL   | 1               | I      | Allows for the choice of two VCO ranges to optimize PLL stability and jitter performance                       |

| MR/OE     | 5               | I      | Allows the user to force the outputs into HIGH impedence for board level test                                  |

| QA (0:4)  | 12, 14, 15,     |        |                                                                                                                |

|           | 18, 19          |        |                                                                                                                |

| QB (0:3)  | 22, 23, 26, 27  | 0      | Clock outputs. These outputs provide low skew copies of REFCLK or can be at different frequencies than REFCLK. |

| QC (0:1)  | 30, 31          |        |                                                                                                                |

| Vcc       | 11, 16, 20, 21, | PWR    | Positive power supply for I/O and core                                                                         |

|           | 25, 32          |        |                                                                                                                |

| PLL_EN    | 9               |        | PLL enable input. When set LOW, PLL is enabled. When set HIGH, PLL is disabled.                                |

| fsel(C:A) | 2, 3, 4         | I      | Frequency control pin                                                                                          |

## DC ELECTRICAL CHARACTERISTICS

TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C, VCC = 3.3V  $\pm 5\%$

| Parameter | Description                                     | Test Conditions | Min. | Typ. <sup>(1)</sup> | Max.      | Unit |

|-----------|-------------------------------------------------|-----------------|------|---------------------|-----------|------|

| Vih       | Input HIGH Level                                |                 | 2    |                     | VCC + 0.3 | V    |

| Vil       | Input LOW Level                                 |                 |      |                     | 0.8       | V    |

| Vон       | HIGH Level Output Voltage                       | Iон = -24mA     | 2.4  |                     |           | V    |

| Vol       | LOW Level Output Voltage                        | Iol = 12mA      |      |                     | 0.3       | V    |

|           |                                                 | Iol = 24mA      |      |                     | 0.55      |      |

| Zout      | Output Impedance                                |                 |      | 14 - 17             |           | Ω    |

| li        | Input Current <sup>(2)</sup>                    | VI = VCC or GND |      |                     | ±200      | μA   |

| Icc       | Maximum Quiescent Supply Current <sup>(3)</sup> | All Vcc pins    |      |                     | 1         | mA   |

| ICCA      | PLL Supply Current                              | Vccapin         |      | 3                   | 5         | mA   |

#### NOTES:

1. For conditions shown as Min. or Max., use the appropriate value specified under recommended operating conditions.

2. Inputs have pull-down resistors affecting the input current.

<sup>3.</sup> Icc is the DC current consumption of the device with all outputs open in high-impedance state and the inputs in its default state or open.

# INPUT TIMING REQUIREMENTS

TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C, VCC = 3.3V  $\pm 5\%$

| Symbol | Description                                           | Description |       | Max. | Unit |

|--------|-------------------------------------------------------|-------------|-------|------|------|

|        |                                                       | ÷4 feedback | 50    | 100  |      |

|        |                                                       | ÷6 feedback | 33.3  | 66.6 |      |

| REF    | Reference CLK input in PLL mode <sup>(1)</sup>        | ÷8 feedback | 25    | 50   | MHz  |

|        |                                                       | ÷12feedback | 16.67 | 33.3 |      |

|        | Reference CLK input in PLL bypass mode <sup>(2)</sup> |             |       | 250  |      |

| dн     | Input clock duty cycle                                |             | 25    | 75   | %    |

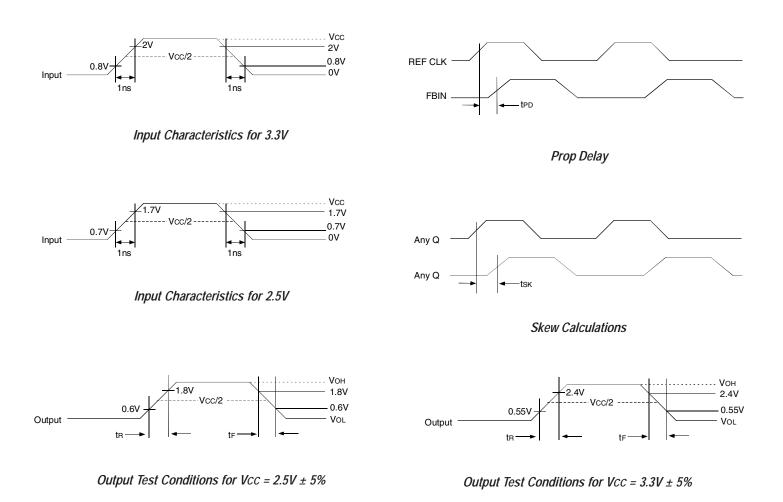

| tR, tF | Maximum input rise and fall times, 0.8V to 2V         |             | —     | 1    | ns   |

NOTES:

1. PLL mode requires  $\overline{PLL\_EN} = 0$  to enable the PLL and zero delay operation.

2. In PLL bypass mode, the IDT5V9352 divides the input reference clock.

## $ACELECTRICAL CHARACTERISTICS^{(1)}$

TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C, VCC =  $3.3V \pm 5\%$

| Symbol        | Characteristic                    | Test Conditions                              | Min.  | Тур.    | Max. | Unit  |

|---------------|-----------------------------------|----------------------------------------------|-------|---------|------|-------|

| tr, tr        | Output Rise/Fall Time             | 0.55V to 2.4V                                | 0.1   |         | 1    | ns    |

|               |                                   | All Outputs, any frequency                   |       |         | 200  |       |

| tsk(0)        | Output to Output Skew             | within Q <sub>A</sub> output bank            |       |         | 200  | ps    |

|               |                                   | within QB output bank                        |       |         | 100  |       |

|               |                                   | within Qc output bank                        |       |         | 100  |       |

| fvco          | PLL VCO Lock Range <sup>(2)</sup> |                                              | 200   |         | 400  | MHz   |

|               |                                   | ÷2output                                     | 100   |         | 200  |       |

|               |                                   | ÷4 output                                    | 50    |         | 100  | Î     |

| <b>f</b> MAX  | Maximum Output Frequency          | ÷6output                                     | 33.3  |         | 66.6 | MHz   |

|               |                                   | ÷8output                                     | 25    |         | 50   | 1     |

|               |                                   | ÷12 output                                   | 16.67 |         | 33.3 | 1     |

| tPW           | Output Duty Cycle                 |                                              | 47    | 50      | 53   | %     |

| tPD           | REFCLK to FBIN Delay              | fref < 40MHz                                 | -200  |         | +150 | ps    |

|               | PLLLocked                         | fref > 40MHz, PLL locked                     | -50   |         | +150 |       |

| <b>t</b> PLZ  | Output Disable Time               |                                              |       |         | 8    | ns    |

| <b>t</b> PHZ  | MR/OE (LOW-HIGH) to any Q         |                                              |       |         |      |       |

| tPZL          | Output Enable Time                |                                              |       |         | 10   | ns    |

| <b>t</b> PZH  | MR/OE (HIGH-LOW) to any Q         |                                              |       |         |      |       |

|               |                                   | Outputfrequencies mixed                      |       |         | 400  |       |

| tı            | Cycle-to-Cycle Jitter             | Outputs in any +4 and +6 combination         |       |         | 250  | ps    |

|               |                                   | All outputs same frequency                   |       |         | 100  |       |

|               |                                   | Output frequencies mixed                     |       |         | 200  |       |

| U(PER)        | Period Jitter                     | Outputs in any ÷4 and ÷6 combination         |       |         | 150  | ps    |

|               |                                   | All outputs same frequency                   |       |         | 75   |       |

|               |                                   | $\div$ 4 feedback divider RMS (1 $\sigma$ )  |       | 15      |      |       |

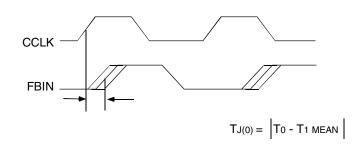

| tJ(φ)         | I/O Phase Jitter                  | $\div$ 6 feedback divider RMS (1 $\sigma$ )  |       | 20      |      | ps    |

| . [,          |                                   | ÷8 feedback divider RMS (10)                 |       | 18-20   |      |       |

|               |                                   | $\div$ 12 feedback divider RMS (1 $\sigma$ ) |       | 25      |      |       |

|               |                                   | ÷4feedback                                   |       | 3 - 10  |      |       |

| BW            | PLL Closed Loop Bandwidth         | ÷6feedback                                   |       | 1.5 - 6 |      | – MHz |

|               |                                   | ÷8feedback                                   |       | 1 - 3.5 |      |       |

|               |                                   | ÷12feedback                                  |       | 0.5 - 2 |      |       |

| <b>t</b> LOCK | Maximum PLL Lock Time             |                                              |       |         | 10   | ms    |

NOTES:

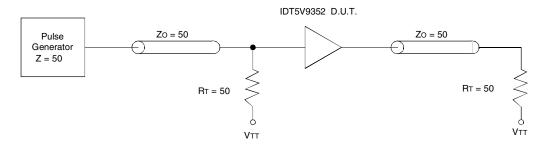

1. AC characteristics apply for parallel output termination of 50  $\Omega$  to VTT.

2. The input frequency on CCLK must match the VCO frequency range divided by the feedback divide ratio FB: freq. = fvco + FB.

# DC ELECTRICAL CHARACTERISTICS

TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C, VCC = 2.5V  $\pm 5\%$

| Parameter          | Description                      | Test Conditions | Min. | Тур. <sup>(1)</sup> | Max.      | Unit |

|--------------------|----------------------------------|-----------------|------|---------------------|-----------|------|

| Vih                | Input HIGH Level                 | LVCMOS          | 1.7  |                     | VCC + 0.3 | V    |

| Vil                | Input LOW Level                  | LVCMOS          | -0.3 |                     | 0.7       | V    |

| Vон                | HIGH Level Output Voltage        | Іон = –15mA     | 1.8  |                     |           | V    |

| Vol                | LOW Level Output Voltage         | Iol = 15mA      |      |                     | 0.6       | V    |

| Ζουτ               | Output Impedance                 |                 |      | 17 - 20             |           | Ω    |

| lı <sup>(2)</sup>  | InputCurrent                     | VI = VCC or GND |      |                     | ±200      | μA   |

| Icc <sup>(3)</sup> | Maximum Quiescent Supply Current |                 |      |                     | 1         | mA   |

| ICCA               | PLL Supply Current               |                 |      | 2                   | 5         | mA   |

#### NOTES:

1. For conditions shown as Min. or Max., use the appropriate value specified under recommended operating conditions.

2. Inputs have pull-down resistors affecting the input current.

3. Icc is the DC current consumption of the device with all outputs open in High-Impedance state and the inputs in its default state (or open).

## INPUT TIMING REQUIREMENTS

TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C, VCC =  $2.5V \pm 5\%$

| Symbol | Description                                           |             | Min.  | Max. | Unit |

|--------|-------------------------------------------------------|-------------|-------|------|------|

|        |                                                       | ÷4 feedback | 50    | 100  |      |

| REF    | Reference CLK input <sup>(1)</sup>                    | ÷6 feedback | 33.3  | 66.6 | MHz  |

|        |                                                       | ÷8 feedback | 25    | 50   |      |

|        |                                                       | ÷12feedback | 16.67 | 33.3 |      |

|        | Reference CLK input in PLL bypass mode <sup>(2)</sup> |             |       | 250  |      |

| dн     | Input clock duty cycle                                |             | 25    | 75   | %    |

| tR, tF | Maximum input rise and fall times, 0.8V to 2V         |             |       | 1    | ns   |

NOTES:

1. Maximum and minimum input reference is limited by the VCO clock range and the feedback divider.

2. In PLL bypass mode, the 5V9352 divides the input reference clock.

# $ACELECTRICAL CHARACTERISTICS^{(1)}$

TA =  $-40^\circ C$  to  $+85^\circ C$  , VCC =  $2.5V\pm5\%$

| Symbol        | Characteristic            | Test Conditions                              | Min.                       | Тур.      | Max. | Unit |  |

|---------------|---------------------------|----------------------------------------------|----------------------------|-----------|------|------|--|

| tR, tF        | Output Rise/Fall Time     | 0.6V to 1.8V                                 | 0.1                        |           | 1    | ns   |  |

|               |                           |                                              | All Outputs, any frequency |           |      | 200  |  |

| tsk(0)        | Output to Output Skew     | within Q <sub>A</sub> output bank            |                            |           | 200  | ps   |  |

|               |                           | within QB output bank                        |                            |           | 100  |      |  |

|               |                           | within Qc output bank                        |                            |           | 100  | 1    |  |

| fvco          | PLL VCO Lock Range        |                                              | 200                        |           | 400  | MHz  |  |

|               |                           | ÷2output                                     | 100                        |           | 200  |      |  |

|               |                           | ÷4 output                                    | 50                         |           | 100  |      |  |

| fMAX          | Maximum Output Frequency  | ÷6 output                                    | 33.3                       |           | 66.6 | MHz  |  |

|               |                           | ÷8output                                     | 25                         |           | 50   |      |  |

|               |                           | ÷12 output                                   | 16.67                      |           | 33.3 |      |  |

| tPW           | Output Duty Cycle         |                                              | 47                         | 50        | 53   | %    |  |

| tPD           | REFCLK to FBIN Delay      | fref < 40MHz                                 | -200                       |           | +150 | ps   |  |

|               | PLLLocked                 | fref > 40MHz                                 | -50                        |           | +150 |      |  |

| tPLZ          | Output Disable Time       |                                              |                            |           | 8    | ns   |  |

| <b>t</b> PHZ  | MR/OE (LOW-HIGH) to any Q |                                              |                            |           |      |      |  |

| tPZL          | Output Enable Time        |                                              |                            |           | 10   | ns   |  |

| <b>t</b> PZH  | MR/OE (HIGH-LOW) to any Q |                                              |                            |           |      |      |  |

|               |                           | Output frequencies mixed                     |                            |           | 400  |      |  |

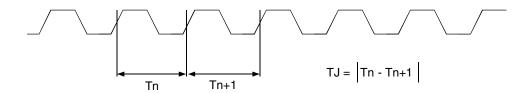

| tı            | Cycle-to-Cycle Jitter     | Outputs in any ÷4 and ÷6 combination         |                            |           | 250  | ps   |  |

|               |                           | All outputs same frequency                   |                            |           | 100  |      |  |

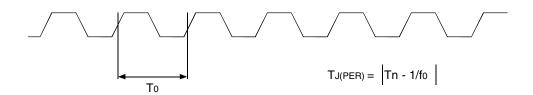

|               |                           | Output frequencies mixed                     |                            |           | 200  |      |  |

| U(PER)        | Period Jitter             | Outputs in any ÷4 and ÷6 combination         |                            |           | 150  | ps   |  |

|               |                           | All outputs same frequency                   |                            |           | 75   |      |  |

|               |                           | $\div$ 4 feedback divider RMS (1 $\sigma$ )  |                            | 15        |      |      |  |

| t)(φ)         | I/O Phase Jitter          | $\div$ 6 feedback divider RMS (1 $\sigma$ )  |                            | 20        |      | ps   |  |

|               |                           | $\div$ 8 feedback divider RMS (1 $\sigma$ )  |                            | 18-20     |      |      |  |

|               |                           | $\div$ 12 feedback divider RMS (1 $\sigma$ ) |                            | 25        |      |      |  |

|               |                           | ÷4feedback                                   |                            | 1 - 8     |      |      |  |

| BW            | PLL Closed Loop Bandwidth | ÷6feedback                                   |                            | 0.7 - 3   |      | MHz  |  |

|               |                           | ÷8feedback                                   |                            | 0.5 - 2.5 |      |      |  |

|               |                           | ÷12feedback                                  |                            | 0.4 - 1   |      |      |  |

| <b>t</b> LOCK | Maximum PLL Lock Time     |                                              |                            |           | 10   | ms   |  |

|               |                           |                                              |                            |           |      |      |  |

#### NOTE:

1. AC characteristics apply for parallel output termination of  $50\Omega$  to  $V\pi.$

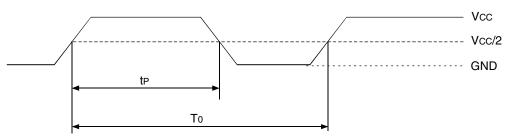

## TEST CIRCUITS AND WAVEFORMS

AC Test Reference for Vcc = 2.5V and Vcc = 3.3V

$tPW = tP/T_0 \times 100\%$

Output Duty Cycle

Cycle-to-Cycle Jitter

Period Jitter

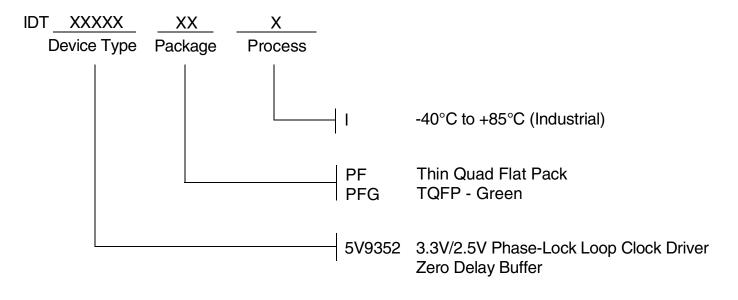

ORDERING INFORMATION

**REVISION HISTORY**

| Rev | Table | Page | Discription of Change                                                                            | Date     |

|-----|-------|------|--------------------------------------------------------------------------------------------------|----------|

| А   |       | 1    | NRND - Not Recommended for New Designs                                                           | 5/20/13  |

| A   |       | 1    | PDN - Product Discontinuation Notice - Last Time Buy Expires<br>October 28, 2014 - PDN# CQ-13-02 | 12/19/13 |

# We've Got Your Timing Solution.

6024 Silver Creek Valley Road San Jose, CA 95138

Sales 800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT Tech Support netcom@idt.com +480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

Copyright 2013. All rights reserved.